# "MICROCOMPUTER CONTROL OF A BLAST FURNACE STOVE MODEL"

PETER BUDIMIR, B.Sc., B.E.(Hon)

BEING A THESIS SUBMITTED

AS PARTIAL FULFILMENT FOR THE

DEGREE OF MASTER OF ENGINEERING SCIENCE

IN THE

DEPARTMENT OF ELECTRICAL ENGINEERING

**APRIL 1983**

THE UNIVERSITY OF ADELAIDE

This thesis embodies the results of supervised project work making up 2/3 of the work for the degree.

# DECLARATION

This thesis contains no material which has been accepted for the award of any other degree or diploma in any University, and to the best of my knowledge it contains no material previously published or written by another person, except where due reference is made in the text of the thesis.

P. BUDIMIR

# ACKNOWLEDGEMENT

Many have been an encouragement and help in the work relating to this thesis. In particular I am grateful to my project supervisors, Dr. D.A. Pucknell and Dr. C.P. Jeffreson for assistance of both technical and non-technical nature.

Thanks go to Telecom Australia for the leave granted to enable me to complete the thesis writing.

There are also a number of other individuals who were of particular help or encouragement; Dr. C.W. Nettle, Mr. N.M. Martin, and Mr. R.W. Korbel who produced the DAC/ADC board and developed stage 2 of the SDK-86 software.

Finally, but most importantly, I would thank my wife, Alison, for invaluable support throughout the project.

### SUMMARY

Because of the large fuel requirements of blast furnace stoves, methods of increasing their operating efficiency are of real practical concern.

This has motivated research into the feasibility of implementing a microprocessor system to control these stoves so as to achieve maximum thermal efficiency. The first phase of this study is the subject matter of this thesis. It involves the initial development of a system to be used for verifying/developing control strategies on an experimental stove model in the Department of Chemical Engineering, University of Adelaide.

The thesis describes,

- (1) basic stove structure,

- (2) operation and control requirements,

- (3) system specifications,

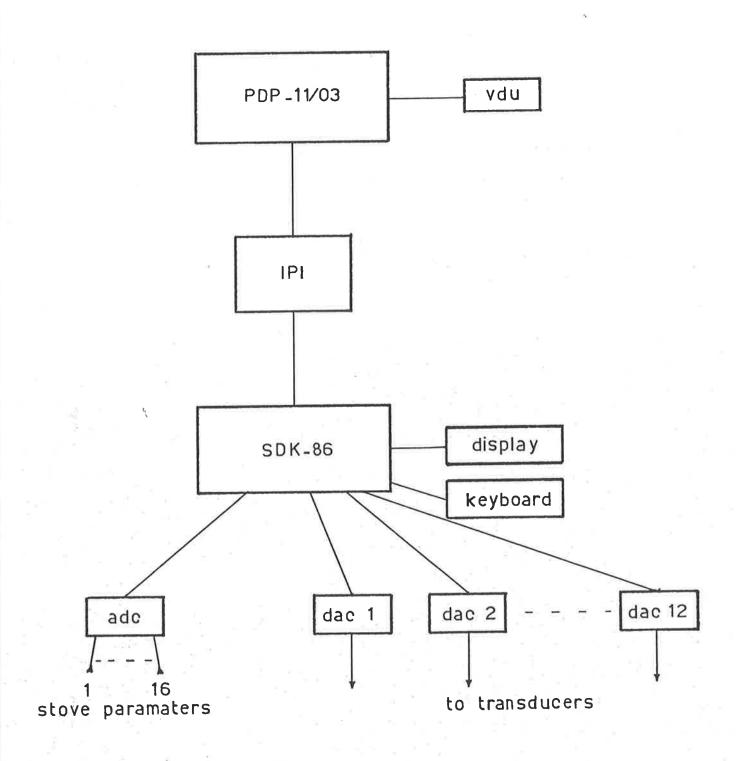

- (4) followed by a description of the microcomputer control system: consisting of an 'upper level' PDP-11/03 microcomputer (DEC) and a 'lower level' SDK-86 microcomputer kit (INTEL).

Hardware design, construction and testing has been completed. A pre-written 'package' has been chosen for the 'upper level' software and 'lower level' software has been developed in two stages. The first stage only involved a single feedback loop for initial hardware tests whereas stage two incorporates the multi-loop system as specified.

| 1. | INTE | RODUCTION                                         | 1    |

|----|------|---------------------------------------------------|------|

| 2. | BLAS | ST FURNACE STOVE OPERATION                        | 3    |

| 9- | 2.1  | INTRODUCTION                                      | 3    |

|    | 2.2  | BLAST FURNACE STOVES                              | 3    |

|    |      | 2.2.1 Introduction                                | 3    |

|    |      | 2.2.2 Stove Description                           | 4    |

|    |      | 2.2.3 Stove Operation                             | - 4  |

|    |      | 2.2.4 Stove Configuration                         | 6    |

|    | 2.3  | EXPERIMENTAL STOVE MODEL                          | 9    |

|    |      | 2.3.1 Introduction                                | 9    |

|    |      | 2.3.2 Description                                 | 11   |

|    | 2.4  | MATHEMATICAL DESCRIPTION                          | 13   |

|    |      | 2.4.1 Introduction                                | 13   |

|    |      | 2.4.2 Analysis                                    | - 14 |

|    |      | 2.4.3 By-Pass Main Operation                      | 17   |

|    |      | 2.4.4 Thermal Efficiency                          | 19   |

|    |      | 2.4.5 Conclusion                                  | 20   |

| 2  | DIA  | ST FURNACE STOVE CONTROL                          | 21   |

| 3. |      | ST FURNACE STOVE CONTROL                          | 21   |

|    | _    | INTRODUCTION                                      | 21   |

|    | 3.2  | CONTROL REQUIREMENTS                              |      |

|    |      | 3.2.1 Introduction                                | 21   |

|    |      | 3.2.2 Switching Period                            | 22   |

|    |      | 3.2.3 Hot Blow Flowrate and Inlet Gas Temperature | 22   |

|    |      | 3.2.4 Zero Changeover Time                        | 24   |

|    |      | 3.2.5 Non-Zero Changeover Time                    | 25   |

|    | 3 3  | CONCLUSTON                                        | 27   |

| 4. 3 | SYST | EM REQUIREMENTS                                       |

|------|------|-------------------------------------------------------|

| 1    | 4.1  | INTRODUCTION                                          |

| 1    | 4.2  | REQUIREMENTS                                          |

|      |      | 4.2.1 Overall Objectives                              |

|      |      | 4.2.2 Computational Requirements (Original Concepts)  |

|      |      | 4.2.3 Computational Requirements (Later Developments) |

|      | 4.3  | PROCESS DESIGN                                        |

|      |      | 4.3.1 Introduction                                    |

|      |      | 4.3.2 Thermal Design                                  |

|      |      | 4.3.3 Flow Control                                    |

|      | 4.4  | OPERATOR/MACHINE INTERFACE                            |

|      |      | 4.4.1 General Requirements                            |

|      |      | 4.4.2 Processor to Processor Interface                |

|      |      | 4.4.3 "Analogue" Transfers                            |

|      | 6    | 4.4.4 Digital Transfers                               |

|      |      | 4.4.5 Priorities and Interrupt Considerations         |

|      | 4.5  | SUMMARY                                               |

| 5.   | PRO  | CESSOR SYSTEM                                         |

|      | 5.1  | INTRODUCTION                                          |

|      | 5.2  | HARDWARE SYSTEM STRUCTURE                             |

|      |      | 5.2.1 Introduction                                    |

|      |      | 5.2.2 PDP-11/03 Microcomputer                         |

|      |      | 5.2.3 SDK-86 Microcomputer                            |

|      |      | 5.2.4 Inter-Processor Interface                       |

|      |      | 5.2.5 Up Transfer                                     |

|      |      | 5.2.6 Down Transfer                                   |

|      |      | 5.2.7 A/D and D/A Convertors                          |

| 5.3 SOFTWARE                                  | 49 |

|-----------------------------------------------|----|

| 5.3.1 Introduction                            | 49 |

| 5.3.2 PDP-11/03 Software (DDACS)              | 49 |

| 5.3.3 SDK-86 Software                         | 51 |

| 5.4 OPERATION - STAGE 1                       | 52 |

| 5.4.1 Introduction                            | 52 |

| 5.4.2 Auto/Manual Transfer                    | 53 |

| 5.5 OPERATION - STAGE 2                       | 55 |

| 5.5.1 Introduction                            | 55 |

| 5.5.2 Operation                               | 57 |

| 5.6 SYSTEM PERFORMANCE                        | 59 |

| 6. CONCLUSION                                 | 60 |

|                                               | •  |

| REFERENCES                                    | 62 |

| APPENDIX A - HARDWARE DESCRIPTION             |    |

| A.1 INTRODUCTION                              |    |

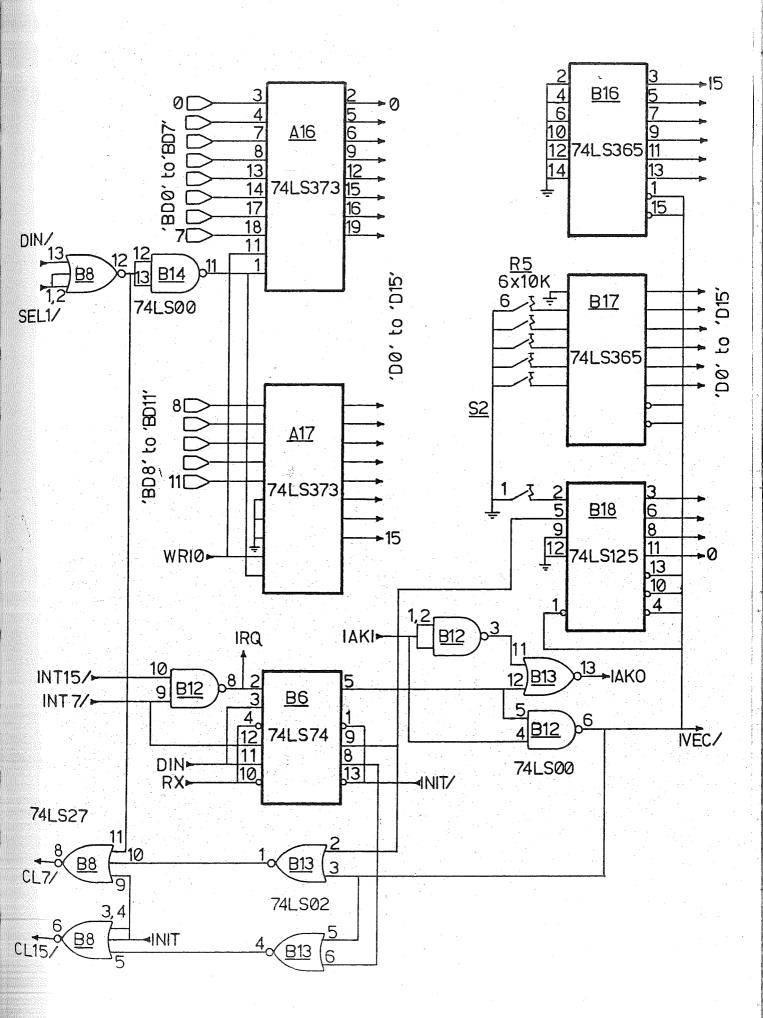

| A.2 INTER-PROCESSOR INTERFACE BOARD           |    |

| A.2.1 BOARD LAYOUT                            |    |

| A.2.2 EDGE CONNECTIONS                        |    |

| A.2.3 ADDRESS DECODING AND BUS INTERFACE      |    |

| A.2.4 UP TRANSFER (CSR AND DBR HARDWARE)      |    |

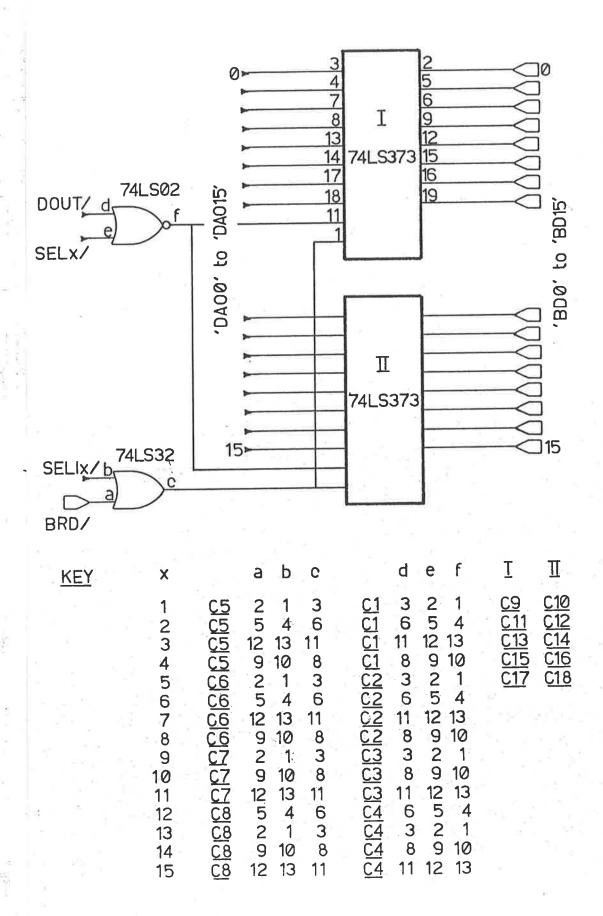

| A.2.5 DOWN TRANSFER HARDWARE                  |    |

| A.2.6 SDK-86 ADDRESSING                       |    |

| A.2.7 PDP-11/03 ADDRESSING AND INTERRUPTS     |    |

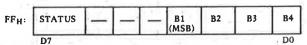

| A.2.8 IPI REGISTER DESCRIPTIONS (CSR AND DBR) |    |

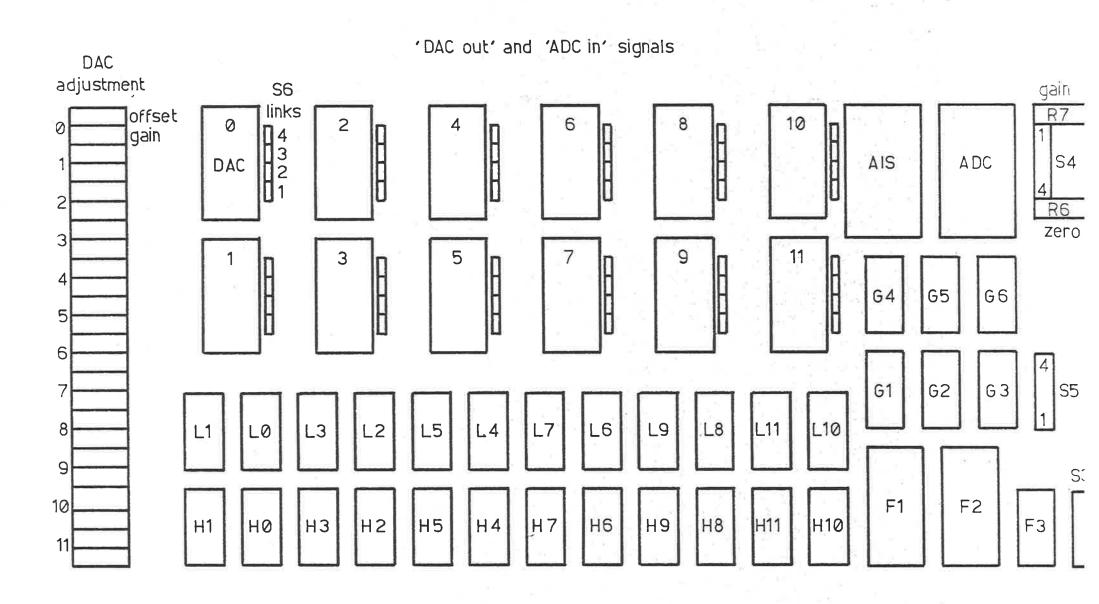

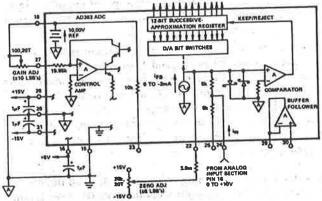

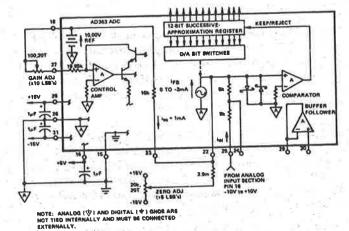

| A.3 DAC/ADC BOARD                             |    |

| A.3.1 BOARD LAYOUT                            |    |

- A.3.2 EDGE CONNECTIONS

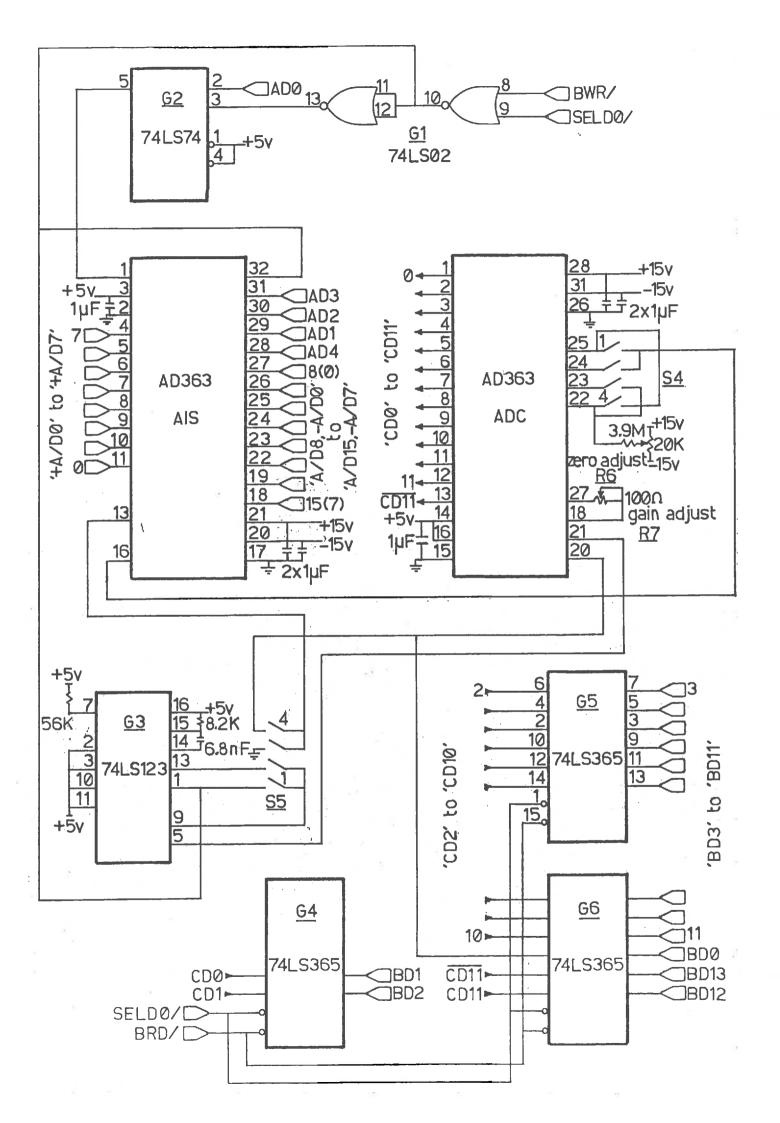

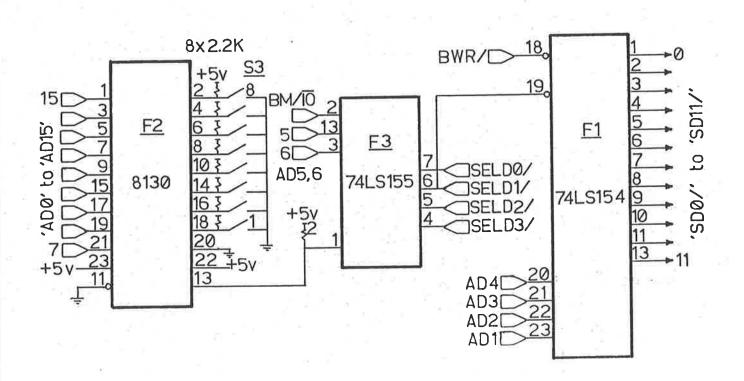

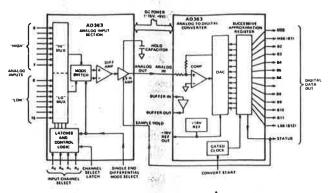

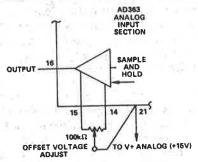

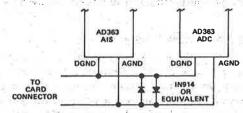

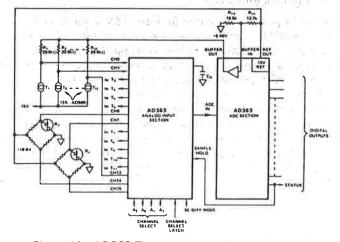

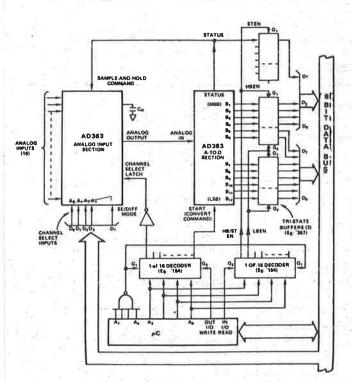

- A.3.3 ADC SECTION HARDWARE

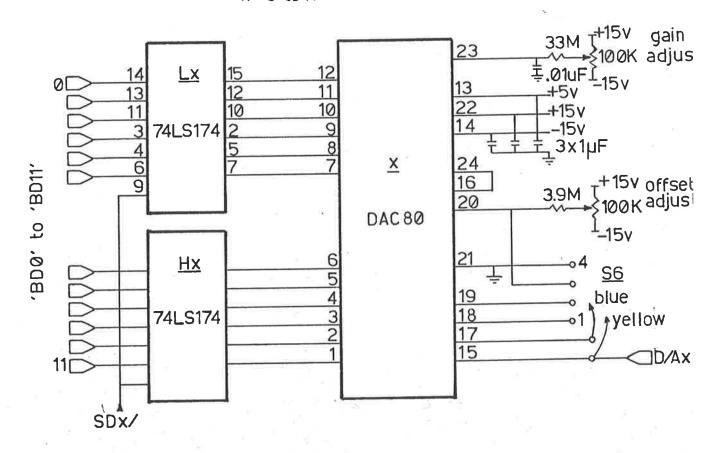

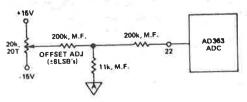

- A.3.4 DAC AND DECODE SECTION HARDWARE

- A.3.5 ADDRESSING

- A.3.6 A/D CONVERSION

- A.3.7 D/A CONVERSION

- A.3.8 ADC RANGE SELECTION

- A.3.9 DAC RANGE SELECTION

- A.3.10 ADC SAMPLING MODE

- A.4 DATA SHEETS (AD363 and DAC80)

- APPENDIX B SOFTWARE DESCRIPTION

- B.1 DDACS DESCRIPTION

- B.2 SDK-86 SOFTWARE LISTING STAGE 1

- B.3 KEYBOARD PARSER STAGE 1

- B.4 SDK-86 SOFTWARE DESCRIPTION STAGE 2

- B.5 SDK-86 SOFTWARE LISTING STAGE 2

# 1. INTRODUCTION

Operation of blast furnaces for iron production requires large 'blasts' of hot air for extended periods of time. Typically, air blast flowrates of 80 to 100 kg/s are necessary, at temperatures of about 1200  $^{\circ}$ C.

This 'blast' is produced by so called Cowper stoves. Because of the huge load requirements of the furnace, it is clear that large quantities of fuel are needed to satisfy the energy demand. It is, therefore, desirable to operate the stove systems as efficiently as possible. Even small increases in stove efficiency can result in large savings in fuel costs.

This has motivated studies into means of improving the thermal efficiency of Cowper stove operation [eg. 5, 6]. However, this problem is a complex one and until the advent of cheap microprocessing and computing elements, no cost effective means existed to implement algorithms to achieve this maximum efficiency.

This project was initiated as a joint effort between the Chemical and Electrical Engineering Departments of the University of Adelaide, to develop a control system for an experimental stove system in the Chemical Engineering Department. This computer based system was required to;

(1) provide a tool for verifying and/or developing control strategies already proposed [eg. 1, 2, 6] and enable testing of the validity of assumptions made in modelling the stove operation and configurations,

(2) possibly form a base for development of an industrial controller. Since the natural response times in the industrial installation are much longer than those of the experimental rig, any scheme that can meet the speed requirements in the laboratory will be adequate for industry.

Note that, as a research tool, it is required that the system be as flexible as possible. It is, therefore, particularly important that the hardware (processors and interface) does not place restrictions on the types of control strategies to be examined. This has led to the choice of a 16 bit low level microprocessor with a parallel interface to the 'high level function' processor.

This thesis is primarily concerned with the 'by-pass main' stove configuration but the control scheme proposed, being computer based, is flexible enough to be later used for studies of 'staggered parallel' operation.

An overview of this work can be found in the author's joint paper presented at the IE Aust Conference on Microprocessors 1979 [3].

### 2. BLAST FURNACE STOVE OPERATION

#### 2.1 INTRODUCTION

There were two considerations in designing the control system;

- (1) firstly, and most importantly, a useful tool was required by the Chemical Engineering Department to enable research into control mechanisms to be carried out using experimental stove models,

- and (2) of lesser importance, a scheme that could be adapted to actual blast furnace stove control was desirable.

To understand both the nature and complexity of the required system it is necessary to examine stove structure and operation in some detail. This chapter describes both the industrial and experimental stoves and gives a basic mathematical description of the control problem.

#### 2.2 BLAST FURNACE STOVES

### 2.2.1 Introduction

The first regenerative blast furnace stove was developed in 1860 by E. A. Cowper of Scotland. Although much has been done since to improve the effectiveness of these Cowper stoves (as they are commonly known), the essential operating scheme and stove structure have remained unchanged since they were first introduced.

Stove description and operation is well covered in the literature [eg. 4, 5].

# 2.2.2 Stove Description

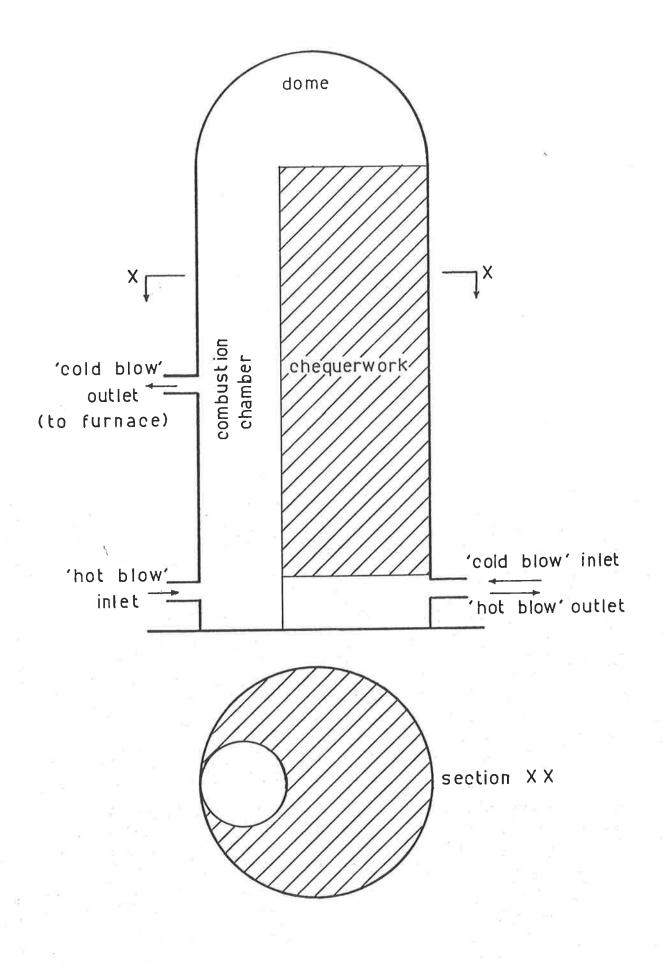

Today's Cowper stoves typically produce air blast flow rates of 80 to 100 kg/s at temperatures of about 1200 °C. A cross-sectional diagram of a stove is shown in figure 2.1. From this the stove can be seen to consist essentially of:

- (1) a chequerwork This is a large mass of solid material containing many flues through which air can be forced. It performs the heat storage function of the stove and is usually a type of refractory brick. Typically the chequerwork is about 20 m to 30 m high and about 8 m in diameter, weighing of the order of 1 million kg. The efficiency and thermal capacity of the stove are governed by the surface area of the brick chequers and their mass respectively.

- (2) a combustion chamber Blast furnace gas (fuel) is burnt with air at the base of this chamber. The hot gas can then be forced up the chamber and down through chequerwork.

# 2.2.3 Stove Operation

The operation of a Cowper stove involves two distinct phases:

- (1) the heating period During this phase hot gas is forced up through the combustion chamber and down through the chequerwork. Heat is thus transferred from the gas to the chequerwork. This process is often referred to as the 'on gas' phase of the cycle or, in academic circles, the 'hot blow' period.

- (2) the cooling period This is the phase in which the

Stove Cross Section FIGURE 2.1

stove actually supplies the hot air blast to the furnace (i.e. the 'on blast' part of the cycle). Cold air is forced up through the chequerwork and is thus heated and exits the stove as a hot blast. This is often referred to as the 'cold blow' part of the cycle.

# 2.2.4 Stove Configuration

It is clear from the above description that one stove is not sufficient if a continuous hot blast is required, since the chequerwork will cool during the 'cold blow' cycle. Eventually the outlet blast temperature will no longer be sufficient to supply the blast furnace requirement.

Thus two or more stoves are necessary. While one (or more) is 'on blast' the others are in their heating phases. By 'switching' the stoves at appropriate times the required continuous blast is maintained.

Since the outlet temperature of the 'cold blow' stove will drop in time, some mechanism must exist to provide a fixed blast temperature at a given flow rate. At present two main stove configurations exist to meet this requirement:

(1) the 'staggered parallel' system - This is the more efficient [5] but typically requires four stoves (a minimum of three). Operation is described in [5] and basically involves two stoves 'on blast' at any one time. These two stoves are 'staggered' in that one is further into its cycle than the other. Thus the outlet temperatures will be different. By controlling the percentage of air passing

through each of the two stoves the outlet temperature can be held at the required value. Eventually the 'coldest' of the 'on blast' stoves is switched with the 'hottest' of the 'hot blow' stoves. This process continues cyclically.

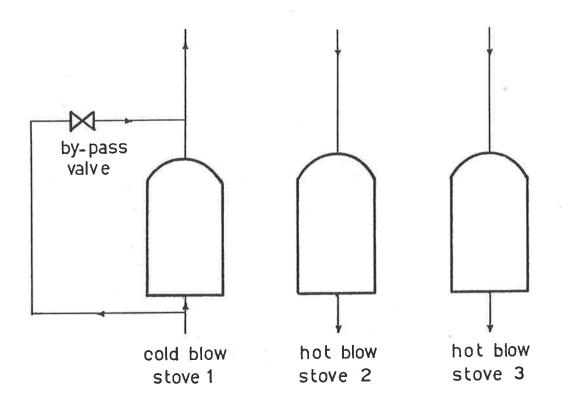

(2) the 'by-pass main' system - This is the older of the two configurations and for economic reasons is still preferred by the majority of users, in Australia at least. Typically three stoves are used, with two being a minimum. Also being the simpler system, initial control studies will deal with this configuration. Hence it is described in more detail here than the 'staggered parallel' system (unless otherwise stated, further references to stove configuration will assume a 'by-pass main' system).

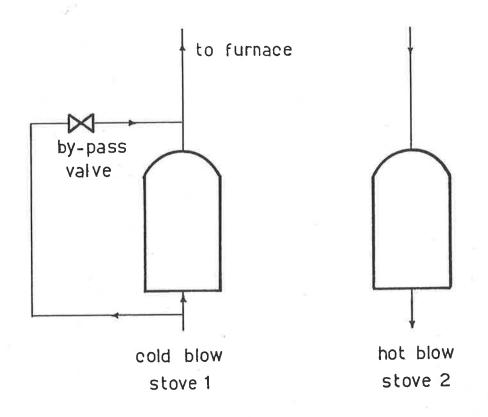

The 'by-pass main' system is well described in [6] and this description is outlined here. Consider first the two stove system of figure 2.2. From the diagram it is seen that stove is 'on blast' at any one time. The required blast flow rate is determined by the flow rate of the cool The temperature is controlled by allowing some of input. the air to by-pass the stove and then mix with the heated air at the stove outlet. At the start of the 'cold blow' cycle, stove outlet temperature and hence the amount by-passing the stove will be at a maximum. the chequerwork cools, the exit temperature will drop and a greater portion of the air will pass through the stove. The limit of this cycle occurs when the exit temperature equals the required blast temperature. At this stage all the air

By-Pass Main Stove Configuration for 2 Stoves FIGURE 2.2

flow would pass through the stove. In practice stove switching must occur well before this stage is reached.

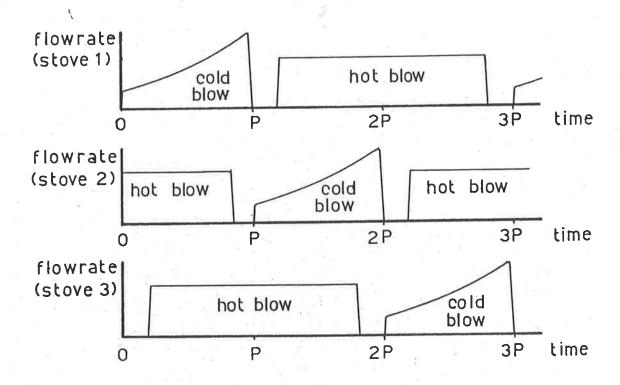

During this process the 'hot blow' stove is being heated in preparation for an 'on blast' cycle. Because of finite switching times this stove must be taken off its current cycle in preparation for 'cold blow' before the 'on blast' stove ends its cycle (see figure 2.2, 2.3).

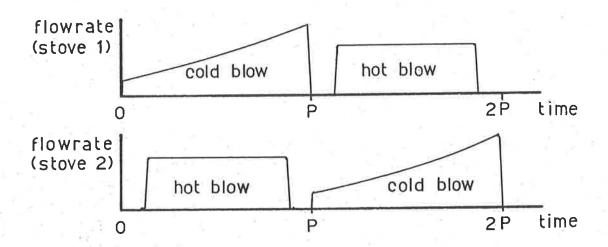

The process is essentially the same for a three be seen from figure 2.3. 'by-pass main' system as can Although further details of the 'by-pass main' configuration will be discussed later, one concept that bears mentioning at this stage is that of 'cyclic equilibrium'. This refers to a dynamic equilibrium of stove operation. Once reached, any one stove will have the same temperature profile (of the at equivalent times in each complete cycle. chequerwork) Note that the 'state' of the stove, at any time, is defined temperature profile, providing the thermal this рv capacitance of the gas is zero.

One key factor in the control problem is determining under which conditions 'cyclic equilibrium' can be established.

### 2.3 EXPERIMENTAL STOVE MODEL

### 2.3.1 Introduction

Because of the massive size of the actual Cowper stoves it is not possible to have these available to test control procedures and study stove operation. Although computer

By-Pass Main Stove Configuration for 3 Stoves

FIGURE 2.3

simulations have yielded some useful results [5, 6] a laboratory test bed is necessary for further investigation. The Chemical Engineering Department has developed such test columns.

Using these, control strategies can be developed and tested. Because the time constants relating to the models are much shorter than those of actual Cowper stoves, any digital control system which can handle the sampling rates required for the model will certainly have adequate capacity for controlling an industrial system.

# 2.3.2 Description

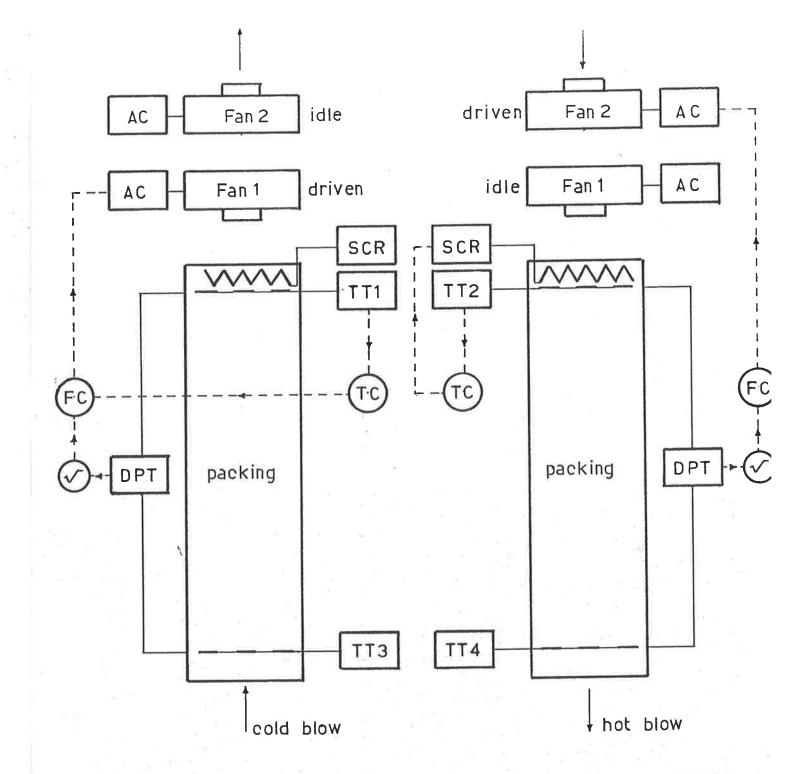

Figure 2.4 shows, diagramatically, the experimental stove system, set up for 'by-pass main' operation.

The left hand stove is heating cold air drawn through As has been seen before, the exit air packing by fan 1. temperature (measured by the temperature transmitter TT1) is Thus to obtain a constant 'blast' falling with time. temperature and flow rate the air leaving stove 1 needs 'mixed' with a cooler 'by-pass' stream (as described in sec 2.2.4). This mixing procedure is not carried out in the experimental set up, but the 'by-pass' effect on the stove can be reproduced using a local flow control loop. achieved using a differential pressure transmitter, be software square root extraction, a Zener Electrics armature current controller and variable speed DC motor. The set point of this loop can be adjusted by the temperature

# KEY

TT: Resistance Bulb Temperature Transmitter

DPT: Differential Pressure Transmitter

TC: Temperature Control Algorithm

FC: Flow Control Algorithm

AC: Armature Current Speed Controller

-+--: Control Flow

control algorithm.

Experiments performed in the Chemical Engineering Department indicate sample rates of the order of 50 Hz will be required if significant degradation in the performance of the flow loops is to be avoided.

The second stove of figure 2.4 is on 'hot blow' using the second blower to force air over a nichrome wire heater with a phase-angle controlled SCR regulator. Experiments on a similar loop indicate that a sample rate of 10 Hz should be satisfactory for the associated temperature control loop.

Flow through the 'hot blow' stove will be initially constant, using a similar fast 'local' flow loop to the 'cold blow' stove.

This system differs from the industrial installation, mainly in the use of electric heating instead of a combustion system. The design is also intended to eliminate parasitic thermal capacitances (which are present in reality) to simplify the control studies. This has largely been achieved by avoiding the use of multiport control valves and by using light, stainless steel, vacuum-jacketted stoves. Fast temperature control loops should also ensure sharp stepwise temperature changes.

### 2.4 MATHEMATICAL DESCRIPTION

### 2.4.1 Introduction

A comprehensive treatment of the principles in heat transfer

has been developed by Jakob. Details of the operation and analysis of regenerators (Cowper stoves fall into this category) can be found in his book on heat transfer [7]. A brief derivation of the equations relevant to stove operation is given below. The nomenclature used has been chosen to be consistent with that adopted by Jeffreson [6].

# 2.4.2 Analysis

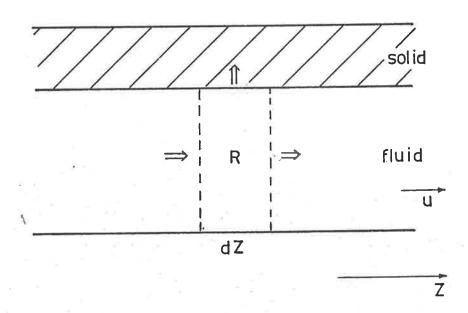

To simplify stove analysis, a one dimensional model (in space) is adopted. This results in distance (z) and time ( $\theta$ ) being the only independent variables in the differential equations.

Figure 2.5 is drawn to reflect this model, and relating to this the following symbols are defined.

- u .. velocity of the fluid (m/s).

- $\rho$  ...density  $(kg/m^3)$ .

- M ..total mass of the chequerwork (kg).

- C .. specific heat/unit mass for solid  $(J/^{\circ}C-kg)$ .

- S ... specific heat/unit mass for fluid  $(J/C^{\circ}-kg)$ .

- k .. thermal conductivity  $(J/m-s-C^{\circ})$ .

- h ..heat transfer coefficient between solid and fluid  $(J/s-m^2-C^\circ)$ .

- a ..cross-sectional area (m2).

- L ..length of chequerwork (or packing) (m).

- 1 ..total contact length (cross-section) (m).

- A ..total perimeter of flues (solid surface area, m2).

- Z ..distance independent variable (m).

- $\Theta$  ...time, independent variable (s).

⇒ heat flow

Heat Transfer Diagram

FIGURE 2.5

T ..temperature of the solid, variable (°C).

t ..temperature of the fluid, variable (°C).

f,s.subscripts refer to fluid and solid respectively. The functions  $T = T(\theta,Z)$  and  $t = t(\theta,Z)$  are to be determined, subject to forcing functions and the initial solid temperature distribution. Referring to figure 2.5, and applying the principle of heat balance, the net heat flow into region R is equal to the heat accumulation in R plus the heat transferred to the solid. Thus the heat balance equation for the fluid can be written,

$$a_f .dZ.k_f .\partial^2 t/\partial Z^2 = a_f . f_f .S.dZ.dt/d\theta + h.l.(t-T).dZ.$$

$$...(2.1)$$

Similarly for the solid,

$$a_s .dZ.k_s .\partial^2 T/\partial Z^2 = a_s. f_s.C.dZ.dT/d\theta + h.l.(T-t).dZ.$$

$$...(2.2)$$

Now we define,

$$z = Z/L$$

... normalised length ...(2.3)

and  $w = \rho_f$  .a<sub>f</sub>.u ... fluid flow rate (kg/s) ...(2.4)

and using  $d/d\theta = \partial/\partial\theta + u.\partial/\partial Z$  for the fluid, and  $d/d\theta = \partial/\partial\theta$  for the solid (since the solid is stationary), equations (2.1) and (2.2) become,

$$\partial t/\partial z = h.A.(T-t)/(w.S) + (k_f.a_f/(w.L.S)).\partial^2 t/\partial z^2 - (L/u).\partial t/\partial \theta$$

...(2.5)

and M.C.

$$\partial T/\partial \theta = h.A.(t-T) + k_s.a_s.L.\partial^2 T/\partial z^2$$

. ...(2.6)

Since the thermal capacity of the fluid is insignificant,

the  $\partial t/\partial \theta$  term in equation (2.5) can be removed. Also, taking typical values of stove paramaters (eg. [5] pp 35, 36) the 2nd order terms become insignificant, giving,

$$\partial t/\partial z = h.A.(T-t)/(w.S)$$

...(2.7)

and M.C. $\partial T/\partial \theta = h.A.(t-T)$ . ...(2.8)

By solving these equations, subject to the relevant boundary conditions, the temperature functions can be determined. The paramaters h, A, M, C and S are characteristics of the stove material and gas. Hence they are not directly controllable by the operator. The inlet gas temperature and flow rate w are the variables that can be altered by the operator to influence stove operation.

# 2.4.3 By-pass Main Operation

Consider now a two stove 'by-pass main' system. Equations (2.7) and (2.8) must be applied separately to the 'hot blow' and 'cold blow' stoves. Using the subscripts 1 and 2 to denote 'cold blow' and 'hot blow' respectively, we have,

for 'hot blow'

$$\partial t_2/\partial z = h_2.A.(T-t_2)/(w_2.S_2)$$

...(2.9)

and M.C.

$$\partial T/\partial \theta = h_2.A.(t_2-T)$$

, ...(2.10)

for 'cold blow'

$$\partial t_{i}/\partial z = -h_{i}.A.(T-t_{i})/(w_{i}.S_{i})$$

...(2.11)

and M.C.

$$\partial T/\partial \theta = h_1.A.(t_1-T)$$

. ...(2.12)

The minus sign in equation (2.11) is necessary since

flow is in the reverse direction for the 'cold blow'.

In addition to these equations, the 'by-pass' control during 'cold blow' results in a flow rate variation as follows (taking  $t_{\rm lin}$  = 0, as the reference temperature),

$$w_1 = \widehat{w} \cdot t_{p} / t_{1x} \qquad \dots (2.13)$$

where,

$\hat{\mathbf{w}}$  is the required blast furnace flow rate,  $\mathbf{t}_{\mathrm{IX}}$  is the stove exit air temperature,  $\mathbf{t}_{\mathrm{B}}$  is the required blast temperature.

This equation assumes that the specific heats of air at  $t_{lx}$  and  $t_{p}$  respectively are equal, and results from a heat balance over the mixing point.

This leaves three operator adjustable variables; the 'hot blow' inlet temperature  $(t_{2in})$ , flow rate  $(w_2)$  and the period P of the operation cycle. Having selected these, equations (2.9) and (2.10) can be solved to give a temperature profile (T) at the end of the 'hot blow'. This then becomes the initial profile in equations (2.11) and (2.12). These can be solved to give the temperature profile at the end of the 'cold blow', thus providing the initial profile for solving the 'hot blow' equations again. By repeating this procedure a 'cyclic equilibrium' is reached where the temperature profile is the same (for a given stove) at the beginning of any given hot or cold blow.

'Cyclic equilibrium' is the normal operating state of stove system and it is important that the operator selects  $w_2$ ,  $t_{2in}$  and P so that equilibrium is possible. If, for example,  $t_{2in}$  is too small, the 'hot blow' stove will not store as much heat as is required. When switched to 'cold blow' it will not be able to meet the blast furnace temperature requirement for the full period P and so the stoves must be 'switched' earlier than desired. Because of this the other stove has had less time on 'hot blow' and thus aquires even less heat than stove 1. Thus the 'switching' period P must be decreased further. This self destructive mechanism will eventually lead to a failure referred to as 'collapse' (reference [8]).

# 2.4.4 Thermal Efficiency

It has been seen that the operator has three controllable variables ( $t_{2in}$ ,  $w_2$ , and P) and providing these are chosen carefully a 'cyclic equilibrium' situation can be reached. It is clearly desirable, however, to choose these in such a way as to maximise the thermal efficiency of the stove system, while satisfying the 'demand' for hot blast air. In fact it would be preferable to be able to develop and implement control algorithms which would automatically achieve this result.

What effect do these variables have on thermal efficiency?

Jeffreson [6] shows that the most efficient operation occurs

by allowing P to 'float' (i.e. the stoves are switched only

when the 'cold blow' stove can no longer meet the blast furnace requirements) and selecting  $w_2 \cdot t_{2 \, ln}$  as small as possible, consistent with 'cyclic equilibrium'.

In the case of zero changeover time this condition is equivalent to minimising the switching period (P).

# 2.4.5 Conclusion

Solving the stove equations is not possible analytically and so numerical methods are needed. Thus some digital computing elements will be necessary to predict and control the above variables to achieve maximum thermal efficiency.

# 3. BLAST FURNACE STOVE CONTROL

### 3.1 INTRODUCTION

Having considered the basic structure and operation of stove systems, the control problem can be now be examined in more detail. Because of the non-linear characteristics of stove system operation, and the nature of the heat transfer equations, any efficiency controls will necessarily involve numerical analysis.

This immediately establishes the need for some form of 'intelligent' digital control system. With the increasing availability and decreasing prices of a wide range of processors (mini and micro) and peripheral equipment, the digital control concept becomes an extremely attractive one.

### 3.2 CONTROL REQUIREMENTS

### 3.2.1 Introduction

Operation of a 'by-pass main' stove configuration involves a number of 'standard' feedback loops. In the case of the experimental stove system these loops can be seen in figure 2.4. They comprise a 'temperature' and a 'flow' feedback loop for both the 'cold blow' and 'hot blow' stoves.

Except for the 'square root' extraction in the flow loops, conventional PID (Proportional Integral Derivative) control is adequate to obtain the desired 'by-pass main' operation.

As has been described in the previous chapter, there remain three variables available for operator adjustment; the switching period (P), the 'hot blow' input gas temperature and flowrate  $(t_{2in}, w_2)$ . It is our concern here to examine in more detail the selection of these variables so as to obtain the maximum thermal efficiency; this can be defined as the ratio of the total heat removed during 'cold blow' to that supplied during 'hot blow'.

# 3.2.2 Switching Period

Two distinct approaches exist in determining P. The first involves the selection of some predetermined value. The second, and more efficient, approach is to allow the period to 'float'. Switching only occurs when the 'cold blow' stove can no longer meet the blast furnace requirements.

In practice, of course, switching must occur before this limit point is reached. A convenient means to cater for this safety margin is to adopt the ratio described in reference [6],

$$K = W_1(P)/\widehat{W}, \qquad \dots (3.1)$$

that is, the fraction of air passing through the 'cold blow' stove at the end of its cycle. The limiting value is clearly one (no safety margin). Thus for a given K value the switching period P is defined; switching is initiated when the 'cold blow' flowrate w reaches  $K.\hat{w}$ .

# 3.2.3 Hot Blow Flowrate and Inlet Gas Temperature

For a two stove system the thermal efficiency during 'cyclic equilibrium' can be written [6],

$$\Omega = \hat{\mathbf{w}} \cdot \mathbf{t_B} / (\mathbf{w_{zavq}} \cdot \mathbf{t_{zin}}) \qquad \dots (3.2)$$

where  $w_{\text{lavg}}$  is the flowrate of the hot gas averaged over the whole cycle. This equation also assumes that all relevant specific heats are equal.

It is clear from this that the product  $w_{2avg}$   $t_{2in}$  must be minimised. Additional to this, a very useful result has been derived by Kwakernaak in [9]. Here it is shown that thermal efficiency during the 'hot blow' is optimised if,

- (1) the inlet temperature  $(t_{2in})$  is set to its maximum value (this is a physical limitation) and,

- (2) the flowrate  $(w_2)$  is held constant during this phase.

At present Jeffreson does not believe condition (2) to be important when the heat transfer coefficient is approximately proportional to the flowrate [13]. In any case, by developing a flexible control system, this and other considerations can be evaluated with the stove model.

In the context of overall operation (heating and cooling) it is not rigorously proved that thermal efficiency is maximum under these conditions. However, Kwakernaak feels from physical considerations that the above criteria should apply.

Thus, summarising these results, the conditions for maximum thermal efficiency can be stated,

(1) set the inlet temperature during 'hot blow' to the

maximum value, consistent with imposed physical limitations and,

(2) set the 'hot blow' flow rate to its minimum constant value so that 'cyclic equilibrium' can still be maintained.

The objective, therefore, of maximum efficiency control is to determine (beforehand) this minimum value of  $\mathbf{w}_2$ , for a given blast furnace loading. Note that finite changeover time means that the actual manipulated hot gas flowrate  $\mathbf{w}_2$  will be greater than the average value  $\mathbf{w}_2$  and which defines the overall thermal efficiency.

# 3.2.4 Zero Changeover Time

For the situation where stove changeover takes zero time, the minimum  $w_2$  can readily be determined as shown in reference [6]. Although the assumption of zero changeover is clearly not valid it is useful in yielding a lower limit value for  $w_2$ .

The approach taken to determine this value is based on the observation that the period (P) approaches zero as  $w_2$  is decreased. Thus the minimum (most efficient)  $w_2$  occurs in the limit as P approaches zero. Applying this criterion to equations (2.7) and (2.8) a solution becomes possible. For the case of a two stove 'by-pass main' system this takes the form (for  $t_{lin} = 0$ , as the reference temperature) [6],

$$t_{B} = t_{zin} \cdot (1-e^{\beta})/(1-x \cdot e^{\beta})$$

...(3.3) where,

$$x = \widehat{w}.S_1/(\overline{w}_2.S_2) \qquad ...(3.4)$$

$$\beta = (x-1).\overline{\Lambda}_1/(1+\overline{h}_1/\overline{h}_2)$$

...(3.5)

and

$$\overline{\Lambda}_{i}$$

, the 'reduced length' is defined as  $\overline{\Lambda}_{i} = \overline{h}_{i} \cdot A/(\widehat{w} \cdot S_{i})$ . ...(3.6)

Here  $\overline{h}_i$  and  $\overline{h}_i$  are reference values of the heat transfer coefficient during 'cold blow' and 'hot blow' cycles respectively.

The above equation can then be solved for  $w_{2min}$  once the values  $\widehat{w}$  and  $t_{n}$  are specified.

# 3.2.5 Non-Zero Changeover Time

Under realistic conditions, of non-zero changeover time, the problem of determining  $w_{2min}$  is considerably more difficult. A number of approaches have been investigated (to some degree) but all have their difficulties.

One approach [6] is to assume that the heat transfer coefficient is proportional to flowrate. Under such conditions, the effect of the 'hot blow' is determined by the area under the ' $w_2$  vs time' graph. Thus if the period is to be halved, the flowrate  $w_2$  need only be doubled to maintain equilibrium. Hence, we can write for a 1-N stove system,

$$W_2 = W_{20} \cdot N \cdot P / (N \cdot P - P_c)$$

...(3.7)

where,

$w_2$  is the actual 'hot blow' flowrate,  $w_{2c}$  is the flowrate for  $P_c = 0$ , and P is the changeover time.

However, not knowing the value of P beforehand means that  $w_{2min}$  cannot be determined from equation (3.7) alone. To overcome this, Jeffreson [6] has used an iterative approach in his stove simulations. This involves adjusting the value of  $w_{2}$  in each new cycle as follows,

$$W_2^{(K+1)} = W_2^{(K)} \cdot \overline{W}_{20} / W_{2avg}^{(K)} \dots (3.8)$$

where,

$$w_{2arg}^{(\kappa)}$$

is the integrated flow of the kth cycle,

and  $\overline{w}_{2o} = w_{2omin} \cdot N.P/(N.P-P_c)$ . ...(3.9)

Note that  $\overline{w}_{20}$  is just the minimum zero changeover value from equation (3.3), adjusted for the new period.

Such an approach, however may exhibit convergence problems. A possible refinement, not yet tried, may be to determine a close starting value for  $w_2$  before applying equation (3.8). Consider first  $w_{20}$  as a linear function of P,

$$W_{20} = W_{20min} .(1+c.P)$$

...(3.10)

This is a good approximation over the normal operating range. The value  $w_{20\,m_{1n}}$  is that determined in section 3.2.4 (the zero changeover case). The constant value 'c' could possibly be determined by simulation.

Further, by taking typical values of P and c (as can be derived from simulation results, eg. reference [6]) it is

found that,

From equations (3.7) and (3.10) the flowrate can be expressed as,

$$W_2 = W_{20 \, \text{min}} \cdot (1 + \text{c.P}) \cdot \text{N.P/(N.P-P_c)} \qquad \dots (3.12)$$

Using the inequality (3.11) this can be minimized with respect to P to give,

$$W_{2,min} = N.P.W_{20}/P_{c}$$

...(3.13)

where  $w_{20}$  is the flowrate defined in equation (3.10), and

$$P = \sqrt{P_c/(N.c)} + P_c/N$$

...(3.14)

The value of  $w_{2m/n}$  from equation (3.13) can then be used as the starting value in equation (3.8).

Another approach is to define thermal efficiency as the heat stored as a fraction of total heat input during any hot blow. Such a definition enables efficiency to be written as a function of the 'hot blow' exit temperature. Thus it becomes feasible that the value of w could be determined by appropriate feedback of this temperature (reference [12]).

# 3.3 CONCLUSION

Because of the complexity of the control problem, suitable schemes (algorithms) are still under investigation and development. Thus the control system needs to be flexible enough to incorporate the

changing control algorithms, and in fact, is to be used in the development and verification of these algorithms.

It is clear that a computer based system is the only means whereby such flexibility can be introduced, as well as providing the means to cope with the problem complexity.

To meet the requirements of speed and flexibility a two level system was designed (described in chapter 5). The 'upper' level microcomputer is to handle higher level functions (such as determining  $w_{2min}$ ) and the required loop control. The 'lower' level microcomputer handles basic I/O control and operator interaction. In fact, during manual control mode, the 'lower' level processor becomes a stand alone system (independent of the 'upper' level processor) by which the operator can manually vary the controlled outputs.

#### 4. SYSTEM REQUIREMENTS

#### 4.1 INTRODUCTION

The following chapter defines the specific requirements of the control system as requested by the Chemical Engineering Department. Key decisions relating to system implementation are included together with their justifications.

The section is summarized with a brief description of the overall system structure chosen to meet the above requirements.

## 4.2 REQUIREMENTS

# 4.2.1 Overall Objectives

The experimental work in blast furnace stove modelling in the Chemical Engineering Department required the following:

- (1) Equipment to yield clear and unambiguous experimental verification of theoretical mathematical models of thermal regenerator system dynamics, particularly under the variable flow conditions which prevail in industrial installations. This part of the work requires only one experimental stove.

- (2) Once the experimental difficulties associated with one stove had been isolated and overcome, a further two or three stoves would be added. At this stage, the focus of the work would transfer from identification and modelling of system dynamics to the longer term objective of testing and extending control strategies for the optimal operation of

stove systems under conditions of variable heat demand.

## 4.2.2 Computational Requirements (Original Concepts)

As can be seen from chapters 2 and 3, the various aspects of stove operation combine to present a complex control problem. This, together with flexibility requirements, suggested some form of real time digital control. The original concept (1979) included a multi-processor system based on the Intel 8080 (as development facilities were available for this series of processor). One processor would be assigned to each stove, with communication proceeding via a common bus and memory area.

This arrangement had the attraction of providing adequate computing power by sharing computation, and also introduces a means of including a degree of fault tolerance (necessary in an industrial system). Each processor could be made capable of taking over the basic functions of another 'failed' processor.

# 4.2.3 Computational Requirements (Later Developments)

In the later half of 1979 the Chemical Engineering Department secured an LSI-11/03 (DEC) computer system together with DDACS (a real time operating system tailored to control applications). Calculation of the expected loop rates and estimation of the desired number of loops to be controlled indicated that the LSI-11/03 processor running DDACS would be sufficient for control of the initial stove system.

This processor and DDACS software was presented to the author virtually as an 'engineering' constraint, in that now it was necessary to tailor the system around these items. A microprocessor interface could now be used for the following purposes:

- (1) Provision of the required number of A/D and D/A channels, allowing for expansion necessary for multiple stoves.

- (2) Provision of bumpless auto/manual and manual/auto transfers with 'loop select' facilities.

Also, changes to DDACS software were to be avoided, since it was originally available only in 'executable image' form.

Although an 8 bit microprocessor could handle standard A/D, D/A and other I/O (input/output) control it was also desirable to be able to perform scaling and perhaps other pre-processing of data. Considering also expansion to multiple stoves, a single 8 bit processor was thought to be inadequate.

released their -8086. 16 bit At this time INTEL is four to ten times more powerful microprocessor. This than the 8080 (throughput varies according to application). addition it provided hardware multiply/divide facilities and so seemed ideal to handle the low level I/O tasks. adequate, processing power meant that the more than flexibility existed for assigning more complex tasks to this level, as required.

Thus a system configuration was chosen consisting of the LSI-11/03 microcomputer as an upper level controller, responsible for high level control and optimising tasks, with the SDK-86 (an 8086 based development kit from INTEL) as a low level I/O processor responsible for A/D and D/A control together with appropriate scaling and 'loop select' and auto/manual control.

#### 4.3 PROCESS DESIGN

## 4.3.1 Introduction

This section briefly describes the design of the experimental stove system insofar as it effects the design of the computer system.

## 4.3.2 Thermal Design

The overall "Process Instrumentation Flow" (PI) diagram has been shown in figure 2.4. In essence the packing is first heated by a stream of hot air (shown flowing down through the stove on the right of the diagram) and then cooled by a flow of cold air which "extracts" the heat from the previous "hot blow".

On an industrial scale, the flow reversals are applied by means of a system of three-way valves on the inlet and outlet. Experience in the Chemical Engineering Department on measurements of "single blow", unidirectional, packed bed dynamics [PhD Thesis, C.P. Jeffreson] showed that, for

small scale equipment, the thermal capacity of three-way valves and even fine wire heating elements prevents application of the sharp, square-wave temperature "waves" assumed by the theoretical model. The slow, long time constant, release or absorption of heat, following the initial step is also a problem. This process (called "tailing") overcome, to a large extent, by can be incorporating a temperature control loop around the heater and three-way valves, thus eliminating long term temperature drift. Nevertheless, oscillation and overshoot significant on the time scale of the thermal time constant of the packing, unless the thermal capacitances of the elements inside the inlet temperature control loop are Furthermore, mechanical problems reduced to a minimum. associated with sealing under high stress conditions would be expected with such solenoid or air-actuated three-way valves.

These considerations and others led to the design of figure 2.4 with two variable speed blowers per stove and an inlet temperature control loop for the hot blow part of the cycle which is closed around a fine wire heater. Because of the speed of response required for this inlet temperature control loop, a sampling interval of about 320 ms was chosen. Degradation in performance occured when the sampling interval was increased significantly above this value.

close control over room was thought that At first it temperature and the absence of large thermal capacitances on the inlet during the "cold blow" would eliminate the need for feedback control over inlet temperature during this part of the cycle. It has been found in practise that for the temperature rise chosen at the heater power available (2 kW) long term variations in temperature do cause room -The most recent design (1982) adds a significant drift. further inlet temperature controller to control the cold blow inlet temperature.

This change serves to illustrate the need for sufficient flexibility and capacity in the control system if it is to be useful as a research tool. This approach differs somewhat when designing for a fixed application (eg. an industrial system) where the control system requirements can be specified more exactly.

# 4.3.3 Flow Control

Since the system involves variable flow control of the cooling air according to the optimal strategies to be devised, variable flow is best achieved by closing the loop around each fan. The differential pressure across the packing becomes the measured variable and the armature current, the manipulated variable. This loop is also "fast" by process control standards; a sampling interval of 80ms has been found necessary to avoid undesirable oscillation and overshoot.

## 4.4 OPERATOR/MACHINE INTERFACE

## 4.4.1 General Requirements

The considerations in the specifications for the operator interface are as follows:

- (1) Because of the time taken for each regenerator to reach equilibrium, the system must be capable of unattended operation for long periods of time.

- (2) It must be possible to start the system with any desired combination of loops on "manual". In this case, it should be possible to independently raise or lower outputs to the final control element of any "manual" loop. Note that the term "loop" in this context is used to refer to any control path (with or without feedback).

- (3) Because of requirement (2) above, automatic, bumpless transfer from manual to automatic operation, and back again is essential.

- (4) Because of the flexibility required of the system in configuring various combinations of feedforward, feedback, cascade and sequencing control, some method is required to associate any given D/A output and/or A/D input channel(s) with any specified control loop or control strategy.

## 4.4.2 Processor to Processor Interface

Given the processor arrangement as discussed in 4.2.3 it is necessary to provide an interface between the LSI-11/03 and the SDK-86. Clearly the simplest means of doing this would be to use a serial communication's link (such as RS232).

This was not acceptable for two main reasons:

- (1) Without abandoning the simplicities inherent in a serial interface such as RS232 the data transfer rate is limited to about 9600 baud. With synchronous operation this is equivalent to 1200 bytes/sec. For a four stove system this would be currently acceptable. However, the system flexibility becomes severely limited, since higher sampling rates and more complex control strategies may be precluded. As such, the system would not be very useful as an investigative, research tool.

- (2) The DDACS control software (for the LSI-11/03) has been designed to work with the standard DEC D/A and A/D boards (AAV11-A and ADV11-A). This involves, essentially, parallel communication. Thus, to use a serial interface, DDACS software changes would be required.

With the above considerations, it was decided that the best approach would be to use an interface that made the SDK-86 look like the standard DEC D/A (communication from LSI-11/03 to SDK-86) and A/D (communication from SDK-86 to LSI-11/03) boards. This involved interfacing the SDK-86 directly onto the LSI processor bus.

Such an approach means that no changes need be made to the DDACS control software and the data transfer speed will be more than adequate. In addition, there is the convenience of being able to treat the SDK-86 as just another (albeit intelligent) DEC peripheral.

Aside from the increase in complexity the approach chosen has one other disadvantage compared to a serial interface. It means that the two processors, must be close to each other. This could prove unsatisfactory in an industrial, distributed system where a number of "low level" processors need to be located remotely from each other.

As well as the main interface described above (the IPI) a "status" interface is required to enable the LSI-11/03 to get necessary "loop" status data (see section 4.4.4).

# 4.4.3 "Analogue" Transfers through the Inter-Processor Interface For a four stove system a minimum requirement is:

- (1) Three analogue inputs per stove (two "temperature transducers" and one "differential pressure transducer").

That is 12 analogue inputs.

- (2) Three analogue outputs per stove (one SCR for temperature control, and two armature current controllers). That is 12 analogue outputs.

# 4.4.4 Digital Transfers through the Inter-Processor Interface

As well as providing the appropriate control and feedback values, the SDK-86 needs to communicate with the LSI-11/03 regarding the operating status of each "loop". This can be done by using the PPI (programmable peripheral interface) of the SDK-86 directly interfaced with the DEC digital I/O unit. The information required by the LSI-11/03 can be encoded into 3 bits as follows:

(1) "Loop" status, auto or manual, using 1 bit.

(2) Two bits to inform the DDACS software of the "change state",

0 0 "Hold"

1 0 "Raise"

0 1 "Lower".

This information would be used by the DDACS system to alter setpoint values and manual control settings, as well as initialising the PI or PID controllers.

## 4.4.5 Priorities and Interrupt Considerations

The clock scheduler of the DDACS operating system is required to ensure that each SCHEME or task runs strictly at the desired sample rate. If delays were to occur, say in performing the A/D or D/A conversions, a "timeout" would follow, resulting in a system halt. Clearly this must be avoided.

It follows that A/D and D/A requests through the IPI to the SDK-86 must be given a high priority through interrupt control. The interrupt control circuitry uses a standard INTEL controller chip. This has been implemented by Mr. R.W. Korbel, together with a software "ring buffer" to stack interrupts when necessary.

Auto/Manual or Raise/Lower requests from the operator may be given a much lower priority. Hence no provision need be made for the SDK-86 to interrupt the DDACS system. Instead, regular polling of the auto/manual and raise/lower status bits by an appropriate DDACS SCHEME will be adequate.

## 4.5 SUMMARY

Summarizing the system, as defined so far, two processor levels can be defined:

- (1) The higher level LSI-11/03 running the DDACS operating control software. This level supervises the various "loops" controlling such things as sampling rates, feedback values auto/manual and manual/auto transitions.

- (2) The lower level SDK-86 which provides the operator interface (via keypad and LED display) and controls the A/D and D/A functions, as well as scaling and any pre-processing (or post-processing) of data. The operator must control the designation of "loops" as well as auto/manual transitions, setpoint values and output to manual "loops".

The interface between the two levels will be functionally divided into two areas:

- (1) The IPI (Inter-Processor Interface) which will provide the high speed parallel communication path for D/A and A/D data and channel select control. This must provide for direct interfacing to the LSI bus so that the SDK-86 "looks" like standard DEC A/D and D/A modules. Thus the DDACS software will be directly compatible with the interface. The SDK-86 must be interruptable by DDACS.

- (2) The "digital" interface which enables the LSI-11/03 to obtain required status information from the SDK-86 (and therefore, from the operator). This involves a direct interface between the SDK-86 PPI (peripheral processor interface) and the DEC digital interface.

## 5. PROCESSOR SYSTEM

#### 5.1 INTRODUCTION

The two level processor system chosen for the control of the experimental stoves is described in this chapter. Essentially it consists of an 'upper level' PDP-11/03 interfacing with a 'lower level' INTEL SDK-86 microcomputer. The higher level control functions are handled by the PDP-11/03 under control of a software operating system called DDACS (Direct Digital Automatic Control System), developed by the Central Electricity Board, NE Region Scientific Services Department [10]. The lower level functions, including the house keeping of the D/A and A/D conversions, are handled by the SDK-86.

Note that the SDK-86 software was developed in two stages. Firstly, a simple, single loop control program was written with a view to testing the hardware and interface functions. In this 'bumpless' auto/manual transfer facility the incorporated at the SDK-86 level. Secondly, as a result of a review of the system specifications (section 4) the software was reviewed. This later work was largely done by Mr. In the stage two system, the auto/manual transfer R. facility was incorporated at the PDP-11/03 level.

The choice of the PDP-11/03 followed the decision to use the DDACS software since it was available (at the time) only in DEC MACRO-11 assembly language. This choice of software followed by processor is a curious turnabout and well illustrates the growing trend to

avoid or minimise software effort. This reflects the increase in software development costs and the relative decrease in hardware costs.

#### 5.2 HARDWARE SYSTEM STRUCTURE

# 5.2.1 Introduction

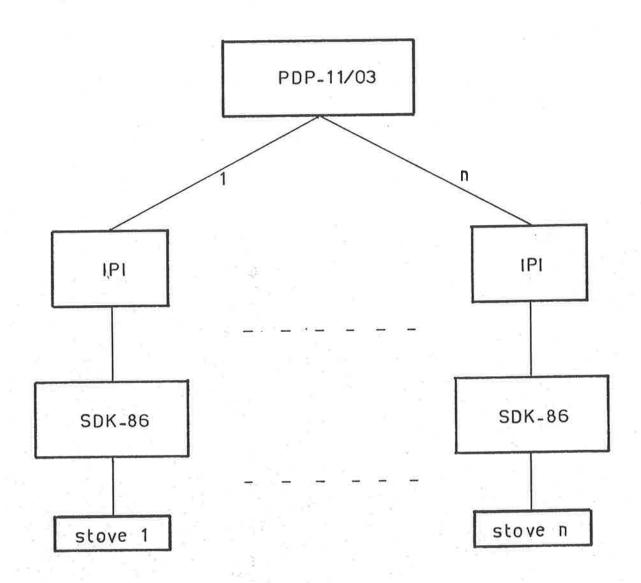

A diagram of the hardware system structure is shown in figure 5.1. From this it can be seen that the structure is hierarchical with the PDP-11/03 acting as a flexible higher level processor. It can handle slower PID control loops, stove sequencing and also supply to the 8086 set points for flow control.

Control over the 16 ADC (analogue to digital convertor) and 12 DAC (digital to analogue convertor) channels is exercised by the 8086, as well as auto/manual and local/remote transfers, and set point ramping and display.

Note that the structure of figure 5.1 is readily expandable to a multi-processor system where the PDP-11/03 oversights IPI several 8086 processors (see figure 5.2). The that each is designed SO (inter-processor interface) another processor can readily be addressed as just peripheral.

Details of all relevant circuits and diagrams have been included in appendix A.

# 5.2.2 PDP-11/03 Microcomputer

This microcomputer is based on DEC's (Digital Equipment)

Control system Configuration

FIGURE 5.1

Multi-Processor Configuration FIGURE 5.2

LSI-11 16 bit microprocessor. The maximum direct address space is 32K words.

A dual floppy disk drive provides the 'mass' storage area and operator interaction occurs via a standard RS-232 serial interface.

Because the assembly language is equivalent to that used in the standard PDP minicomputer series, the system software support is extensive. This will prove useful for further software development at this level. At present the DDACS control software system is to provide the higher level control facilities required. In particular this will include the 'feedforward' control of 'hot blow' flow rate to achieve maximum thermal efficiency.

# 5.2.3 SDK-86 Microcomputer

The SDK-86 is a small design board incorporating the INTEL 16 bit 8086 microprocessor. It has a direct address space of 1 Mbyte and provides sufficient computing power to handle the required 'low level' control of the DACs, ADCs and the setpoint ramping and display. As the system develops further this processor could take more load from the PDP by handling PID loops and also incorporating some degree of digital filtering of the A/D inputs.

A real time control application of the 8086 has already been reported by Newell and Bartlett [11]. Their system involves the use of the 8086 to provide an intelligent interfacing

terminal which can be connected to any multi-user system.

To achieve this flexibility a serial line is used between

the 'host' computer and their 'intelligent' terminal.

This configuration was not possible in our system because of the real time responsibilities of the 'upper' level processor. To provide the necessary speed of communication a parallel inter-processor interface (IPI) was designed.

# 5.2.4 Inter-Processor Interface

The hardware interface has been built to provide a parallel, high speed communications path between the two processors. This inter-processor interface (IPI) enables the PDP-11/03 to control the activities of the 8086, as it would any other device. The difference, of course, is that the 8086 can behave as a highly intelligent peripheral.

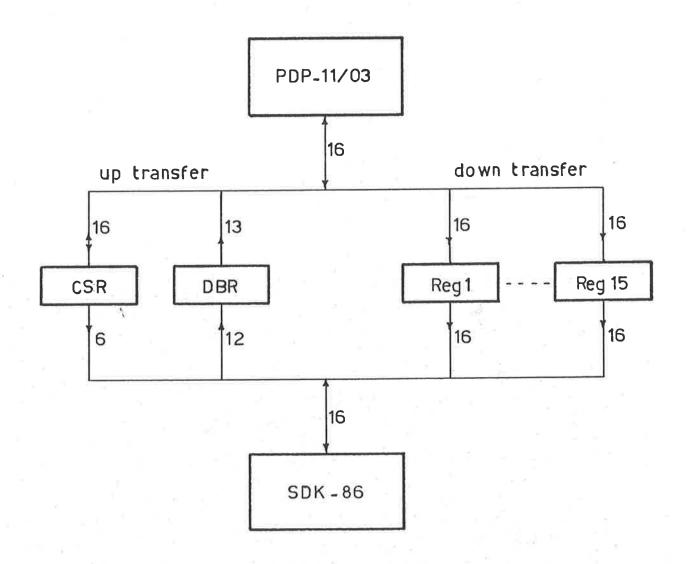

Although the data can be transmitted in both directions the mode of operation differs in each case and is controlled by two distinct sections of the IPI. This is described below with reference to figure 5.3.

The development of the IPI was the most time consuming part of the project, although conceptually simple. Because it is functionally simple the description that follows is short. The hardware details of the functional blocks can be found in appendix A.2.

## 5.2.5 Up Transfer

Data transfer from the 8086 to the PDP-11/03 is in the form

Inter-Processor Interface (IPI)

FIGURE 5.3

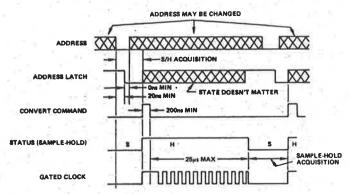

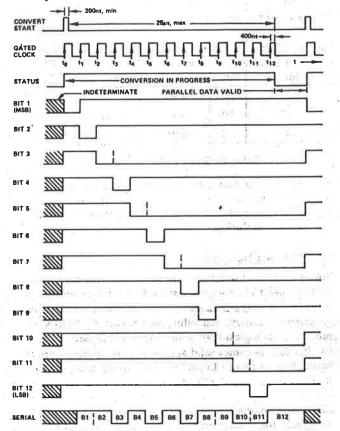

of 12 bit words and is handled by two intermediate IPI registers; the command status register (CSR) and the data buffer register (DBR). Both function in the same way as the CSR and DBR registers in the standard DEC analogue to digital convertor module (ADV11-A). This is a welcome convenience since it means that a programmer familiar with PDP systems is already equipped to write the interface control software.

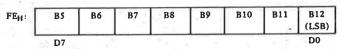

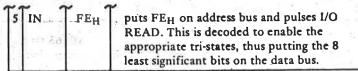

When the PDP requires data from the 8086, it sets bit 0 (least significant bit) of the CSR and sends a channel address (bits 11, 10, 9, 8). This can specify one of 16 channels. The 8086 detects bit 0 set (either on a scan basis, or as an interrupt) and so knows that data is required from the specified channel. This data is written to the DBR (a 12 bit word). When this is received in the DBR bit 7 of the CSR is set and the 'start bit' (bit 0) is cleared.

The PDP can determine that data is available in two ways;

- (1) firstly, it can scan the CSR and test bit 7 or,

- (2) it can 'condition' the transfer to operate on an interrupt basis by previously setting bit 6. In this case bit 7 will generate an interrupt when set.

There is also facility for setting an error flag (bit 15 of the CSR) when the PDP;

(1) attempts to request data before a previous request is honoured or,

(2) fails to read requested data before further data arrives.

Bit 15 can also be made to interrupt the PDP by setting bit 14 (i.e. interrupt on error).

## 5.2.6 Down Transfer

Figure 5.3 illustrates the 'down transfer' section of the IPI. This enables 16 bit words of data to be transferred from the PDP-11/03 to the 8086, along one of 15 separate parallel channels through intermediate registers.

The PDP-11/03 simply writes to each register as a separate memory location whenever it is necessary to send data. There is no direct facility to inform the 8086 when data has been sent, although bits in the CSR could be used for this purpose.

However, this added complexity was not considered necessary. The 8086 need only treat these registers as the source of predefined (by software) parameters and data which it reads as necessary (eg. flowrate value). The PDP-11/03 is left responsible for updating these registers.

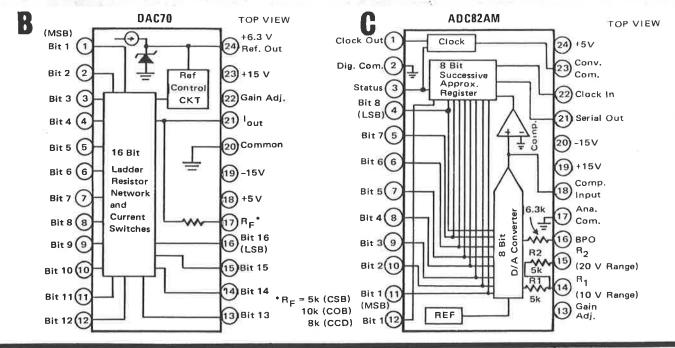

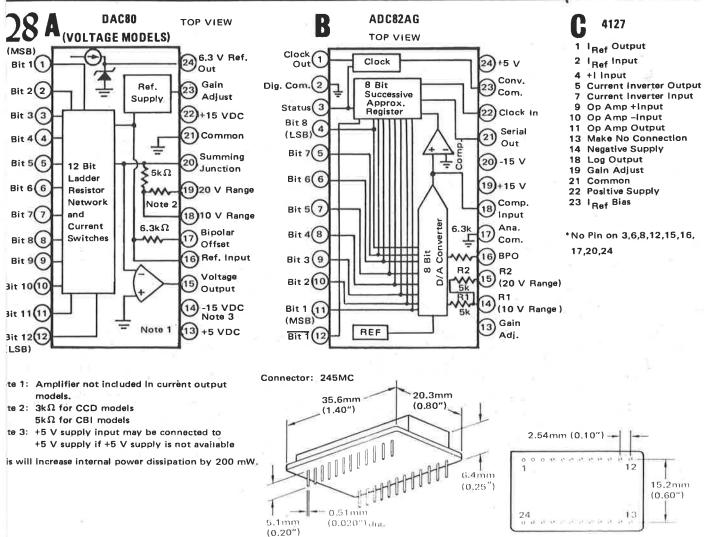

# 5.2.7 A/D and D/A Convertors

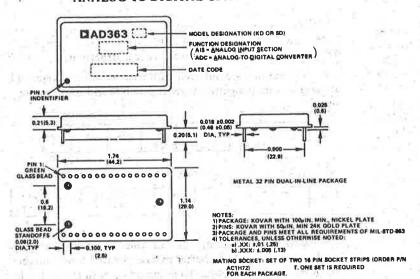

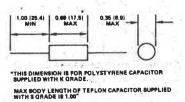

For a full four stove system 12 A/D and 12 D/A channels would be required. To meet these requirements Analogue Device's AD363 data acquisition system was chosen to perform the A/D conversions and Burr-Brown DAC80 D/A convertors were chosen to perform the D/A function (see appendix A.4 for the

relevant data sheets).

Both devices are 12 bit convertors and have been incorporated on one SBC-80 board (INTEL standard). The hardware details, including addressing information etc. has been included in appendix A.

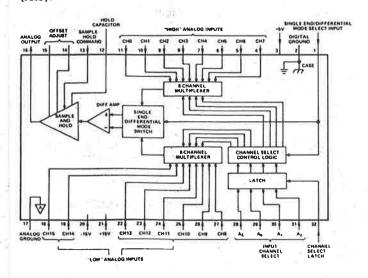

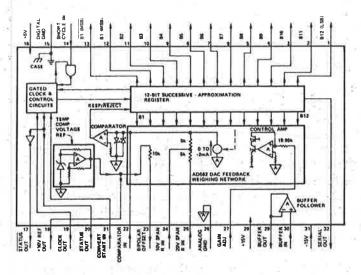

The AD363 includes a 16 channel multiplexer and control logic to provide 16 single-ended or 8 differential inputs. Its throughput is typically 30kHz, thus meeting the necessary speed requirements.

#### 5.3 SOFTWARE

## 5.3.1 Introduction

From the hardware structure described, it can be seen that two software 'packages' are required. For the PDP-11/03 a software operating system called DDACS (Direct Digital Automatic Control System) was employed. As has been mentioned, this has been developed by the Central Electricity Board, NE Region Scientific Services Department as a general purpose operating system for control applications.

# 5.3.2 PDP-11/03 Software (DDACS)

A detailed description of DDACS, including operating instructions, can be found in the manual written by the software authors [10]. A summary of DDACS operation and facilities has been incorporated in appendix B.1. Essentially it is a self-contained operating system designed

to utilise a 'building block' concept to implement general purpose control systems in a fairly straight forward manner.

The operating system includes a 'real time executive with clock scheduler, an editor and the DDACS compiler. Using the editor the building 'blocks' (in the main these are simply calls to subroutines from a standard library) can be linked together to form a 'loop' which runs at a specified time rate. Any number of these control 'loops' can be brought together in a 'scheme'. While selected 'schemes' are running the operator can be constructing/altering other 'schemes' as a background function.

There are 70 'blocks' available for building the control loops and include the usual arithmetic and logic operators, an integrator, a first order lag and an absolute PID controller block, input/output blocks and functions such as SQRT, SIN, COS, EXP etc.

As well as the facility to reconfigure 'schemes' while on-line, DDACS provides a number of other useful features; full propagation of data errors in a fail safe manner, automatic sequencing of 'loops' of different period and the capability to prevent reset or integral wind-up and to ensure bumpless manual/auto transfer.

Although a machine independent version of DDACS is under development (in CORAL 66) the current version was written in DEC MACRO-11 assembly language. Hence the choice of 'high

level' processor.

# 5.3.3 SDK-86 Software

The first version of the SDK-86 software (stage 1) was written to handle one control loop only, to enable simple testing of the hardware and processor interaction. The auto/manual transfer facility was incorporated at this level during stage 1. The software was written in PLM-86 (a high level block structured language developed by INTEL) and was designed using a 'state machine' approach. Each keyboard entry is assigned a number which acts as a pointer in the current 'state' of the 'parser table'. The entry in this table determines the next 'state' to enter and the required action to be taken (if any). A listing of the software and a description of the 'parser table' are included in appendices B.2 and B.3.

By appropriate keyboard selections the operator can;

- (1) examine the setpoint value (or transducer input if in manual) as a percentage of full span,

- (2) change the above values in selected increments or decrements,

- (3) perform auto/manual transfers.

The software was written to incorporate the algorithms as describe in section 5.4.

Stage two of the SDK-86 involved a total revision of the software to more accurately reflect the newly defined

specifications (chapter 4). Again it was developed using PLM-86 (largely by Mr. R. Korbel). Because of the existing comprehensive facilities provided by DDACS the auto/manual transfer facility was incorporated at the higher level in stage two. Software description and listings are included in appendices B.4 and B.5.

## 5.4 OPERATION - STAGE 1

## 5.4.1 Introduction

The operator, under normal conditions, interacts with the control process via the keyboard and 8 digit display of the SDK-86. The keyboard will be used to select control loops, to display and, if necessary, alter set points (when in auto mode) or loop outputs (when in manual mode). The actual keyboard operation required to accomplish the above functions, under the current software, is detailed in appendix B.

The selection of auto or manual modes (described below) is also accomplished via this keyboard.

When the 'feedforward' control procedure is incorporated (thermal efficiency control) the operator will also be able to use the keyboard to select 'local' or 'remote' operating schemes for 'hot blow' auto loops. Under 'local' mode, the 'hot blow' flowrate set point is set by the operator. Under 'remote' mode it will be provided by the PDP-11/03 in accordance with its 'feedforward' calculations.

The 8 digit display on the SDK-86 board is used to indicate the operating mode and the set point or regulator output value.

# 5.4.2 Auto/Manual Transfer

The existence of the auto/manual option serves two functions. It provides a convenient facility for 'start up' of the control system by enabling the operator to manually bring the stoves into an acceptable operating region before switching to auto control. Secondly, once auto operation is achieved, individual loops can be singled out for manual control when desired; this manual back-up is essential in an industrial system in case of failure of the higher level control functions.

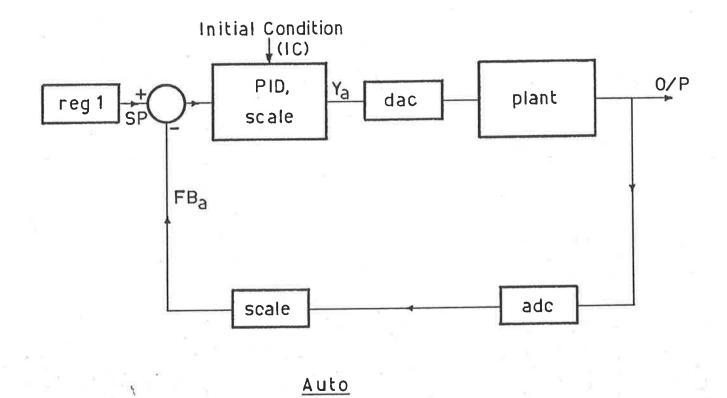

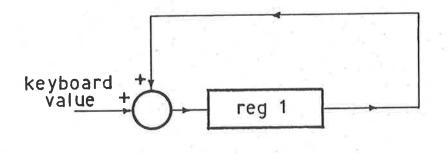

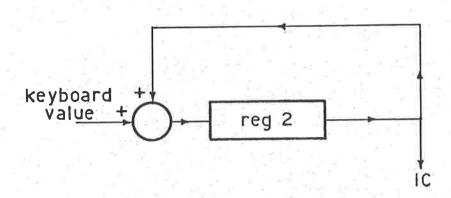

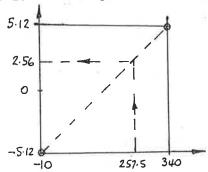

In order to understand operation in each of the modes, consider figure 5.4. During auto operation a set point value (SP) is taken from reg 1. This becomes the input of a single feedback control loop.

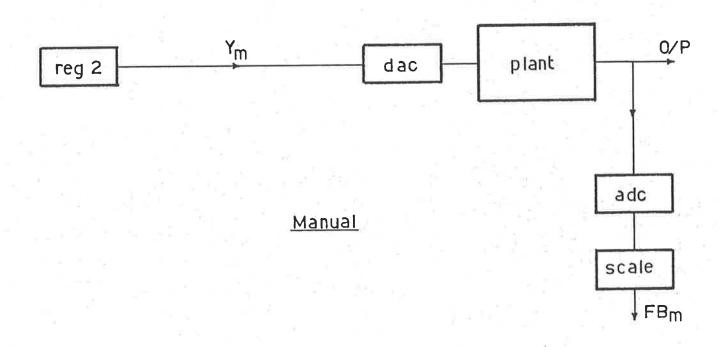

During manual operation the input (taken from reg 2) directly controls the output to the 'final control element'.

There is no feedback as in the auto case.

The problem then presents itself as to how switching between the two modes is to be accomplished. The essential of such a transfer is that there be no 'jump' in the plant output. In some analogue controllers this 'bumpless' transfer is dependent upon the operator properly adjusting set points

Auto/Manual Operation FIGURE 5.4

before switching. It is clearly more desirable to make smooth transition independent of what the operator may do.

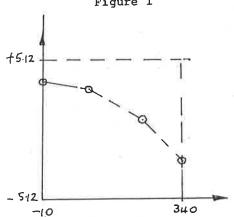

The simple, yet effective, scheme of figure 5.5 was developed to deal with this. Essential to this scheme is the method adopted to change set points (reg 1 and 2 contents). Rather than loading a set point value directly into the registers (reg), a value (entered via the SDK-86 keyboard) is used to increment or decrement their contents.

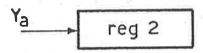

When in auto mode (figures 5.4 and 5.5)  $Y_a$  is continually used to update reg 2. Thus when a switch is made to manual, reg 2 contains the last PID output which then becomes the plant input. This means that the plant input is unchanged during transfer.

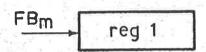

During manual operation  $Y_m$  is used to update the PID block IC (initial condition) and  $FB_m$  is used to update reg 1. This ensures that, when transfer back to auto is made, the output of the plant is unchanged and the error input to the PID block is zero. Thus again 'bumpless' transfer is accomplished.

#### 5.5 OPERATION - STAGE 2

# 5.5.1 Introduction

This software was developed largely by Mr. R. Korbell. It is relevant to this thesis, however, in that it forms part of the overall system as originally conceived. Also, it has made it possible to confirm the feasibility of the system

Auto

Manual

Auto/Manual Transfer FIGURE 5.5

for use as a 'control research tool'.

Again the operator interacts via the keypad, as in stage 1. This stage of software, however, enables multiple loops to be controlled. Basically the operator assigns a 'loop number' to a DAC and ADC channel (not necessarily the same channel numbers). In this way a given control loop can be identified by such a 'loop number'. Having done this, set points can be examined and changed and auto/manual transfer can be initiated.

The DDACS 'loops' must of course be configured in manner consistent with the SDK-86 'loop' assignments.

All loop processing (i.e. determination of DAC output values in a feedback loop, auto/manual transfer and any higher order processing) is still, of course, done by DDACS.

# 5.5.2 Operation

The low level process control is done using the keypad on the SDK-86. Three levels (or modes) of operation exist:

- (1) The Select Mode. This is the 'highest' level mode. Basically, it provides the operator the means to enter either of the other modes (channel or loop). This is accomplished as follows;

- press "," to toggle between the 'channel' select state and the 'loop' select state (not mode),

- press a digit to define the 'channel' or 'loop' number of interest,

- press "." to enter the mode as defined above.

- (2) The Channel Mode. This mode is always associated with a particular channel number as defined in the 'Select Mode'. From here the operator can examine the percentage span or hexadecimal value of the specified DAC (output value) or ADC (input value). This is done as follows;

- press ":" to toggle between percentage span and hexadecimal display,

- press "," to toggle between ADC and DAC display.

In addition the following commands are available;

- press "+" to examine the next channel,

- press "-" to examine the previous channel,

- press "." to return to the 'Select Mode'.

In each case the variables being displayed (including the channel number) are identified on the display.

- (3) The Loop Mode. This mode is always associated with a particular loop number as specified in the 'Select Mode'. From here the operator can assign any ADC and DAC channel to the current loop. In addition auto/manual transfer and setpoint changes can be effected. The commands are as follows;

- press "+" to raise the setpoint (ramp),

- press "-" to lower the setpoint (ramp),

- press ":" to cancel the raise or lower functions,

- press "REG" to initiate the 'loop assignment' procedure; this is followed by "DAC channel number",

- ".", "ADC channel number", "." to complete the assignment,

- press "," to toggle between 'auto' and 'manual' loop status,

- press "." to return to the 'Select Mode'.

In each case the variables being displayed are identified on the LED display.

## 5.6 SYSTEM PERFORMANCE

Although exhaustive tests have not been performed on the system the criteria specified in chapter 4 have all been met. In particular, the throughput of the IPI is sufficiently high to cope with the maximum input/output capability of the PDP-11/03.

## 6. CONCLUSION

A basic system structure for control of a laboratory model of a blast furnace stove has been designed and developed. The hardware has been built and tested. The IPI is sufficiently fast so as not to limit PDP-11/03 input/output speed.

Stage 2 of the software is complete and has enabled initial loop tests to be tried, demonstrating the feasibility of the system.

The result has been that sufficient processing power and interface speed is available to produce a flexible research tool that can readily handle more demanding control applications.

The system configuration chosen is such that it can readily be adapted to a multiprocessor system of one low level microcomputer per stove; this would be the recommended approach for an industrial installation. In addition, the processing power of the 8086 lends itself to the possibility of further processing of data at the low level. Facilities that could be added include;

- (1) handling some local PID loops,

- (2) noise filtering of A/D input data,

- (3) testing for validity of input data,

- (4) limiting inputs and performing other functional mapping.

In retrospect, a number of observations can be made with regard to the project. Firstly, because of the time extent of the work, technological progress in the electronics industry makes some of the choices seem inappropriate. For example, the 8086 processor was the

only 16 bit microprocessor on the market at the time of decision. Since then, new developments have made other processors available which may have proved more appropriate (eg. the MC68000, see reference [14]).

However, this problem is characteristic of any longer term development in this field.

Secondly, a need exists for a rebuilding of the hardware (IPI and the D/A, A/D boards). The prototypes have proven the validity of the design (in light of the specifications) but are a definite maintenance liability. The preferred approach would be to develop printed circuit board assemblies.

#### REFERENCES

- 1. J. Beets, H. Elshout and G. deJong, "Computer Control of a Hot Blast Stove System," Journal A (Belgium), vol. 18, no. 1, pp 31-37, 1976.

- C.P. Jeffreson, "A Computer Control System for Blast Furnace Stoves," Seventh Australian Conference on Chemical Engineering, pp 22-24, Aug. 1979.

- 3. P. Budimir and C.P. Jeffreson, "Microprocessor Control of an Experimental Stove System," Conference on Microprocessor Systems, pp 107-110, Nov. 1979.

- 4. J.C. Buker and N.F. Simcic, "Blast Furnace Stove Analysis and Control," ISA Trans., vol. 2, pp 160-167, 1963.

- 5. H. Kwakernaak, P. Tijssen and R.C.W. Strijbos, "Optimal Operation of Blast Furnace Stoves," Automatica, vol. 6, pp 33-40, 1972.

- 6. C.P. Jeffreson, "Feedforward Control of Blast Furnace Stoves," Automatica, vol. 15, pp 149-159, 1979.

- 7. M. Jakob, "Heat Transfer," vol. 2. New York: John Wiley, 1957.

- 8. P. Zuidema, "Non-stationary Operation of a Staggered Parallel System of Blast Furnace Stoves," Int. J. Heat Mass Transfer, vol. 15, pp 433-442, 1972.

- 9. H. Kwakernaak, R.C.W. Strijbos and P. Tijssen, "Optimal Operation of Thermal Regenerators," IEEE Trans. Automatic Control, vol. 14, pp 728-731, 1969.

- 10. L.R. Johnstone, C.R. Marsland and S.T. Pringle, "A Distributed Computer Control System for a 120 MW Boiler," Proc. Intern. Conf. on Distributed Computer Control (Inst. Elec. Engrs. London), pp 114-119, 1977.

- 11. R.B. Newell and E.G. Bartlett, "A Computer Independent Real-Time Process Interface Unit for Multi-User Computers," Aust. Jl. Inst. Control, pp 56-60, June 1979.

- 12. C.P. Jeffreson, "Dynamic Simulation of Thermal Regenerator Systems under Variable Flow Conditions," accepted for publication subject to revision, The Chem. Eng. Jl., 1981.

- 13. Personal Communication.

- 14. R.D Grappel and J.E. Hemenway, "A Tale of Four MPU's: Benchmarks Quantify Performance," EDN Magazine, April 1, 1981.

APPENDIX A HARDWARE DESCRIPTION

## APPENDIX A

## A.1 INTRODUCTION

The 'lower level' processor and associated hardware reside on three boards;

- (1) the SDK-86 comes on a single board,

- (2) the ADC, DACs and decoding hardware resides on a standard SBC-80 board,

- (3) the IPI resides on a standard SBC-80 board.

These all fit into a four slot carriage with a common back plane which shares the SDK-86 signals (described in A.2.2).

The power supplies are separate units.

A.2 INTER-PROCESSOR INTERFACE BOARD

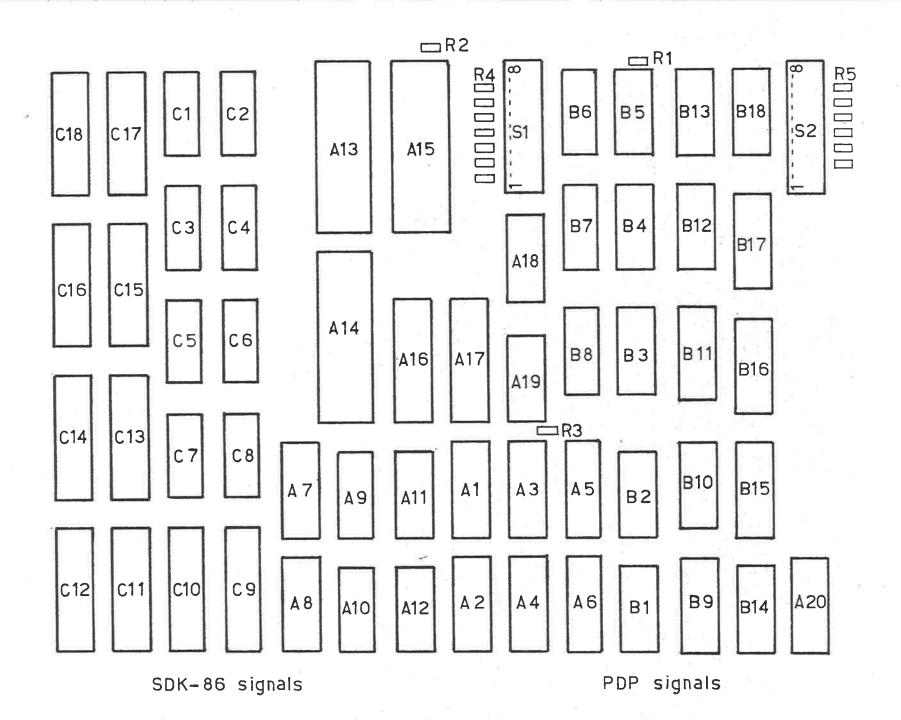

A.2.1 BOARD LAYOUT

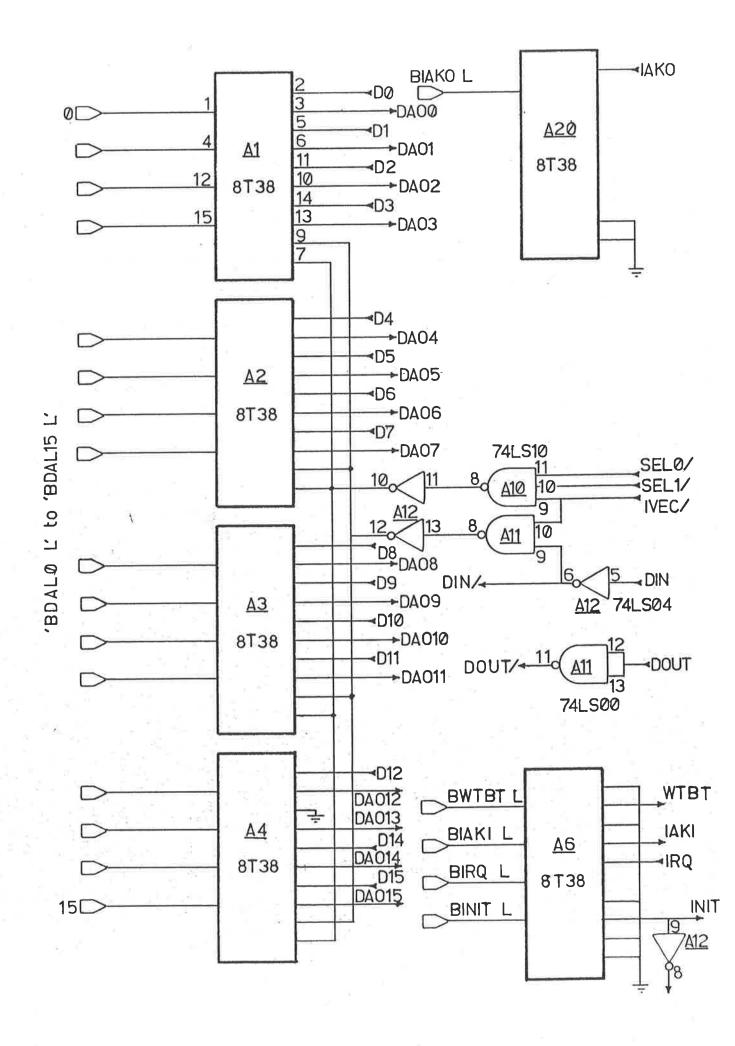

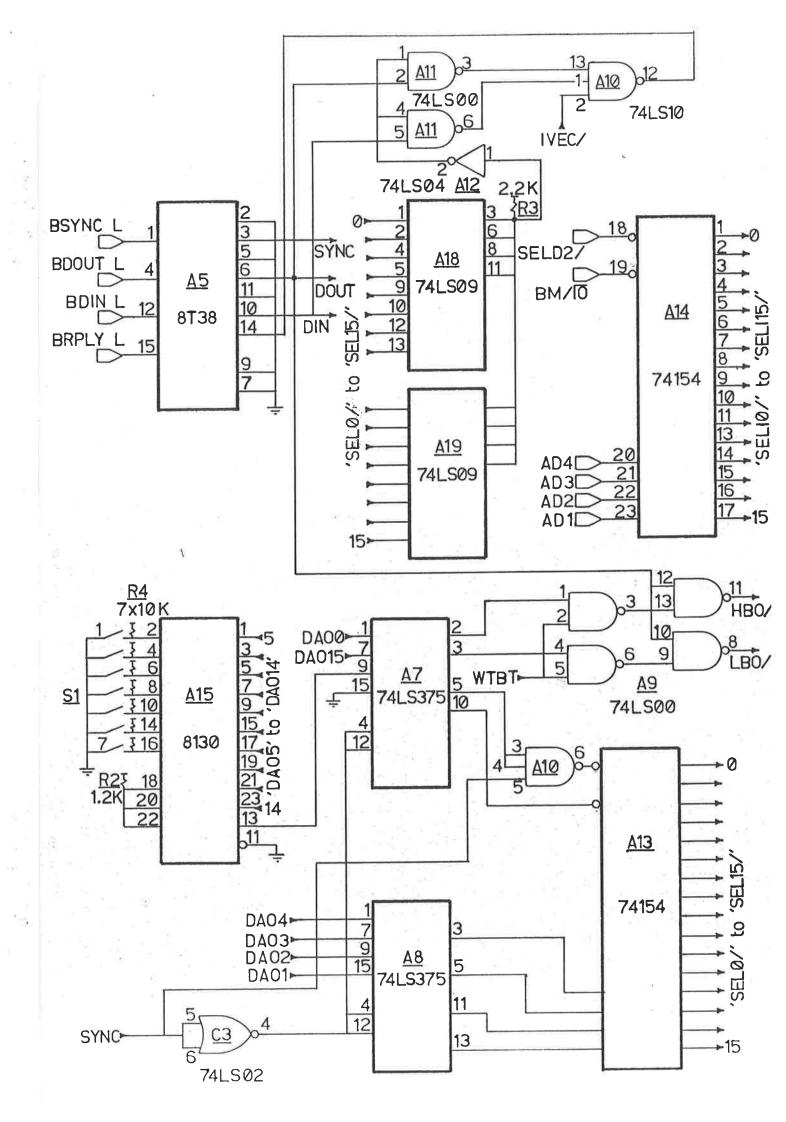

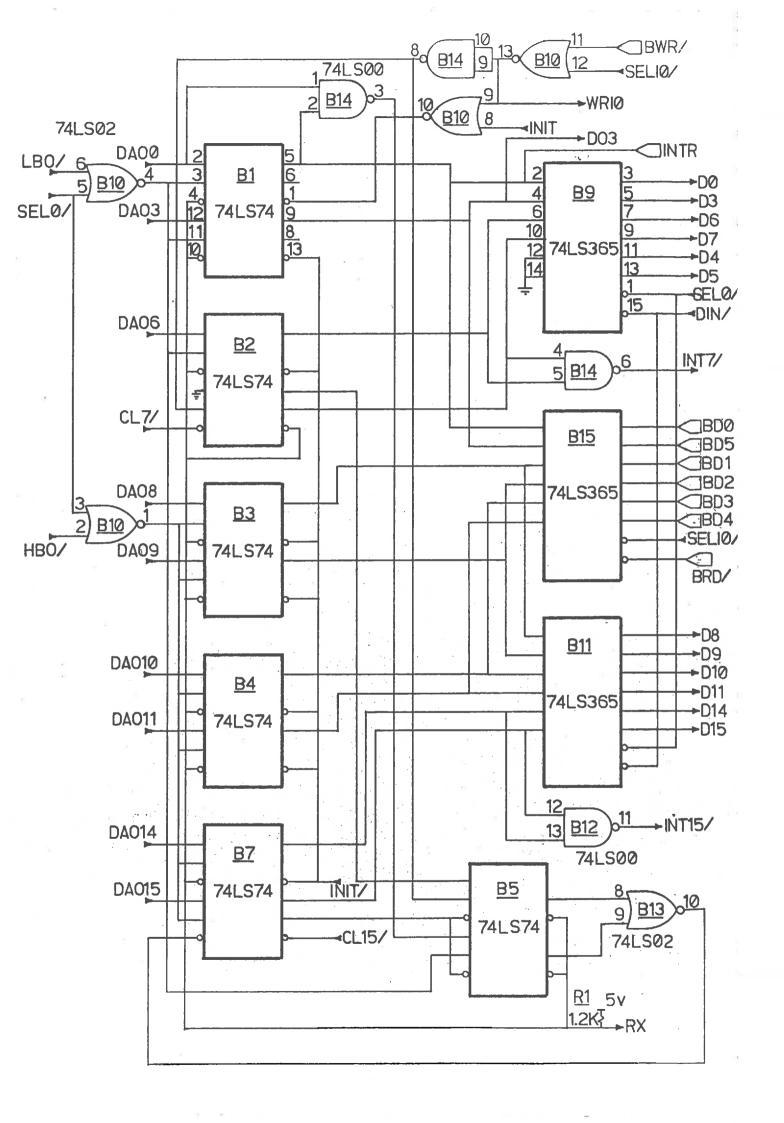

## A.2.2 EDGE CONNECTIONS

## PDP SIGNALS

| PIN NUMBER                                                  | SIGNAL                                                                                                      | PIN NUMBER                                                   | SIGNAL                                                                                                                       |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1<br>5<br>9<br>13<br>17<br>21<br>25<br>29<br>33<br>37<br>41 | BDALO L BDAL2 L BDAL4 L BDAL6 L BDAL8 L BDAL10 L BDAL12 L BDAL12 L BDAL14 L BWTBT L BRPLY L BSYNC L BIAKI L | 3<br>7<br>11<br>15<br>19<br>23<br>27<br>31<br>35<br>39<br>43 | BDAL1 L BDAL3 L BDAL7 L BDAL9 L BDAL11 L BDAL13 L BDAL15 L BDAL15 L BDAL15 L BDAL15 L BDAL15 L BDOUT L BDIN L BIRQ L BINIT L |