# The Study of Trace Cache Memory on Superscalar DLX Processor

Apisake Hongwitayakorn

Thesis submitted for the degree of

Master of EngineeringScience

Department of Electrical and Electronic Engineering

Adelaide University

South Australia

5005

June, 2003

## **Contents**

| Lis | st of Figures                              | •    |

|-----|--------------------------------------------|------|

| Lis | st of Tables                               | vii  |

| Ab  | ostract                                    | viii |

| Ac  | Acknowledgements                           |      |

| 1   | Introduction                               | 1    |

|     | 1.1 Overview                               | 1    |

|     | 1.2 Superscalar Architecture               | 2    |

|     | 1.3 Trace Cache Memory                     | 3    |

|     | 1.4 Contribution of the Thesis             | 4    |

|     | 1.5 Outline of the Thesis                  | 4    |

| 2   | Background                                 | 5    |

|     | 2.1 Overview                               | 5    |

|     | 2.2 Trace Cache Architecture               | 7    |

|     | 2.2.1 The trace cache                      | 8    |

|     | 2.2.2 The fill unit                        | 8    |

|     | 2.2.3 The branch predictor                 | 8    |

|     | 2.2.4 The instruction cache                | 9    |

|     | 2.3 Related Works                          | 9    |

|     | 2.3.1 The trace cache history              | 9    |

|     | 2.3.2 Other high bandwidth fetch mechanism | 14   |

|     | 2.4 Conclusion                             | 16   |

| 3 | <b>Experimental Processor Model</b>              | 18 |

|---|--------------------------------------------------|----|

|   | 3.1 Overview                                     | 18 |

|   | 3.2 DLX Architecture Summary                     | 18 |

|   | 3.2.1 DLX registers                              | 19 |

|   | 3.2.2 DLX data types                             | 19 |

|   | 3.2.3 DLX addressing modes                       | 19 |

|   | 3.2.4 DLX instruction types                      |    |

|   | 3.3 The Superscalar DLX Model                    | 20 |

|   | 3.4 The Fetch Unit                               | 22 |

|   | 3.5 Conclusion                                   | 25 |

| 4 | Experimental Setup                               | 26 |

|   | 4.1 Trace Cache in the Superscalar DLX Processor | 26 |

|   | 4.2 Trace Cache Line Size                        | 28 |

|   | 4.3 Trace Cache Model Components                 | 28 |

|   | 4.3.1 Instruction gathering unit                 | 28 |

|   | 4.3.2 Fill-buffer                                | 29 |

|   | 4.3.2.1 Fill-buffer configuration                | 29 |

|   | 4.3.2.2 Fill-logic and fill-policy               | 31 |

|   | 4.3.3 Trace cache memory                         | 33 |

|   | 4.3.3.1 Trace cache memory structure             | 33 |

|   | 4.3.3.2 Buffer-cache transfer                    | 35 |

|   | 4.3.4 Trace cache hit logic                      | 36 |

|   | 4.4 Benchmarking Programs                        | 38 |

|   | 4.5 Simulation Testbench Configuration           | 40 |

|   | 4.6 Measuring the Trace Cache                    | 40 |

|   | 4.7 Conclusion                                   | 41 |

| 5 | Results                                          | 42 |

|   | 5.1 Overview                                     | 42 |

|   | 5.2 Hits and Misses of the Trace Cache           | 43 |

|   | 5.3 Percentage of Trace Cache Hits and Misses    | 56 |

|   | 5.3.1 Trace cache hits                           |    |

|   | 5.3.2 Trace cache misses                         |    |

|   | 5.4 Trace Cache Space Usage                   | 62  |

|---|-----------------------------------------------|-----|

|   | 5.4.1 Results of <i>TC_4</i> and <i>TC_8</i>  | 62  |

|   | 5.4.2 Analysis                                | 62  |

|   | 5.5 Conclusion                                | 63  |

|   |                                               |     |

| 6 | Conclusion                                    | 65  |

|   | 6.1 Summary                                   | 65  |

|   | 6.2 Conclusions                               | 65  |

|   | 6.3 Further Work                              | 66  |

|   |                                               |     |

| A | Companion CD-ROM Contents                     | 68  |

|   | A.1 DLX Sourcecode                            | 68  |

|   | A.2 Test Programs                             | 69  |

|   | A.3 Simulation log files                      | 69  |

| _ |                                               | 71  |

| В | VHDL Code of Trace Cache                      | . – |

|   | B.1 Dlx.vhd                                   |     |

|   | B.2 DlxPackage.vhd                            | 87  |

|   | B.3 Environment.vhd                           | 88  |

| C | Excerpts from log files of DCT                | 89  |

| D | Runtime Startup Code and Perl Script Listings | 90  |

# **List of Figures**

| 1.1 | Organization of superscalar architecture.                  | 2  |

|-----|------------------------------------------------------------|----|

|     |                                                            |    |

| 2.1 | Trace cache overview                                       |    |

| 2.2 | Trace cache architecture diagram.                          |    |

| 2.3 | The trace cache fetch mechanism.                           |    |

| 2.4 | A loop contains 3 segments                                 |    |

| 2.5 | The trace cache fetch mechanism.                           |    |

| 2.6 | The Branch Address Cache.                                  |    |

| 2.7 | Collapsing Buffer.                                         | 16 |

|     |                                                            |    |

| 3.1 | Big Endian byte ordering.                                  |    |

| 3.2 | DLX instruction format                                     |    |

| 3.3 | Superscalar DLX structure                                  |    |

| 3.4 | Instruction cache structure.                               |    |

| 3.5 | Address-translation and cache-access                       |    |

| 3.6 | Branch-target-buffer structure.                            | 25 |

|     |                                                            |    |

| 4.1 | Trace cache placement in the superscalar DLX machine       | 28 |

| 4.2 | Fill-Buffer structure composes of Trace Information and    |    |

|     | Trace Content.                                             | 30 |

| 4.3 | Anatomy of Trace Information and Trace Content             | 30 |

| 4.4 | Trace cache memory structure.                              | 33 |

| 4.5 | Trace information portion of the trace cache memory        | 34 |

| 4.6 | Trace cache line selector is extracted starting from bit 3 |    |

|     | of the address word.                                       | 35 |

| 5.1a | Hits and misses | s of the trace cache and the instruction cache on bs-a    | 44   |

|------|-----------------|-----------------------------------------------------------|------|

| 5.1b | Hits and misses | s of the trace cache and the instruction cache on bs-r    | 44   |

| 5.1c | Hits and misses | s of the trace cache and the instruction cache on bs-d    | 45   |

| 5.1d | Hits and misses | s of the trace cache and the instruction cache on $pn-20$ | 45   |

|      |                 | s of the trace cache and the instruction cache on $pn-50$ | 46   |

| 5.1f | Hits and misses | s of the trace cache and the instruction cache on pn-100  | 46   |

| 5.1g | Hits and misse  | s of the trace cache and the instruction cache on Permute | 47   |

| 5.1h | Hits and misse  | s of the trace cache and the instruction cache on $DCT$   | 47   |

| 5.2  | Comparison be   | etween TC hit and Compulsory Miss and                     |      |

|      | Conflict Miss   | of DCT                                                    | 52   |

| 5.3  | Hit and miss c  | omparison between $TC_4$ and $TC_8$ at the same cache     |      |

|      | capacity of     |                                                           |      |

|      | (a) <i>bs-a</i> |                                                           | 54   |

|      | (b) <i>bs-r</i> |                                                           | 54   |

|      | (c) <i>bs-d</i> |                                                           |      |

|      | (d) pn-20       |                                                           |      |

|      | (e) pn-50       |                                                           |      |

|      | (f) pn-100      |                                                           |      |

|      | (g) Permute     |                                                           |      |

|      | (h) <i>DCT</i>  |                                                           |      |

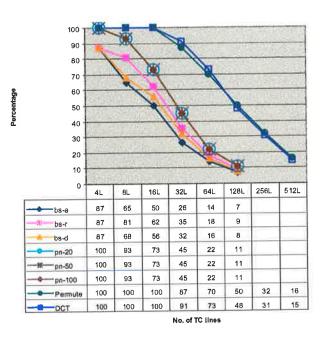

| 5.4  | Percentage of   | total trace cache hit of TC_4 and TC_8                    | 57   |

| 5.5  |                 | TC First Tag Hit of TC_4 and TC_8                         |      |

| 5.6  |                 | TC Line Content Hit of TC_4 and TC_8                      |      |

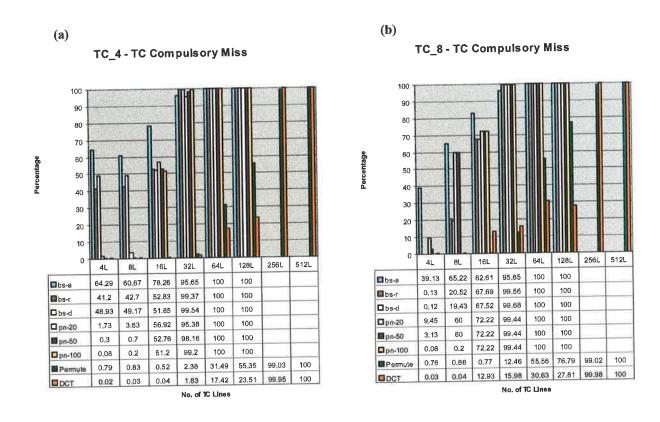

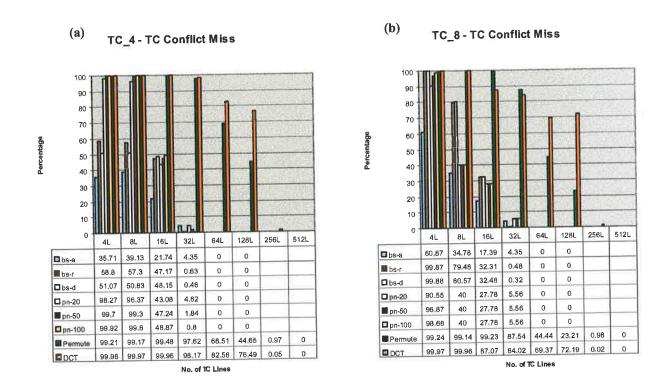

| 5.7  | Percentage of   | TC Compulsory Miss of TC_4 and TC_8                       | 61   |

| 5.8  | Percentage of   | TC Conflict Miss of TC_4 and TC_8                         | 61   |

| 5.9  | TC4 – Percen    | tage of Cache Space Usage                                 | . 62 |

| 5 10 | ) TC8 _ Percen  | tage of Cache Space Usage                                 | . 62 |

## **List of Tables**

| 5.1 | Trace cache hits comparison table of bs-r on TC_4      | 49 |

|-----|--------------------------------------------------------|----|

| 5.2 | The equivalent cache capacity of different trace cache |    |

|     | configurations.                                        | 53 |

### **Abstract**

Instruction-level parallelism (ILP) is a technique to increase processor performance through the simultaneous execution of multiple instructions. Superscalar processor architectures implement ILP by providing multiple execution units to process instructions in parallel. To achieve high performance, the execution units must be occupied by a continuous series of instructions. Hence, the front-end of the processor has to be expanded in order to supply a continuous stream of instructions for the execution units. Although instruction-cache memory has been successfully used to enhance the fetch mechanism of superscalar processors for years, it cannot perform well enough for contemporary processors because of the nature of the statically ordered instructions stored in the cache. Branch instructions are the major problem because of the two possible directions of the branch outcome. They break up the continuity of the static code into short run-length basic blocks. Therefore, a line of an instruction cache can contain instructions that might be abandoned if they follow a branch that will be taken.

Trace cache architecture has been developed to reduce the effect of the problem. It has a sophisticated logic unit to capture dynamic instruction traces, possibly including multiple basic blocks, and store them in a single line. Therefore, it is most likely able to supply a larger segment of useful instructions in one hit. Moreover, the trace cache was deliberately designed not to lengthen the processor pipeline. It has been shown that trace cache can outperform instruction caches in large-scale microprocessors, e.g. 16-instruction wide processors.

This research studies the effect of trace cache memory on smaller-scale microprocessors like the superscalar DLX model that can process only 2 instructions simultaneously. The study will investigate the performance of the experimental trace cache compared to the existing instruction cache and also investigate the trade-offs in varying trace cache size.

To my parents,

my wife, my family, my incoming child,

and everyone who believes in me.

This work contains no material which has been accepted for the award of any other degree or diploma in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text.

I give consent to this copy of my thesis, when deposited in the University Library, being available for loan and photocopying.

Signed: \_

Date: 19 / 06 / 2003

(Apisake Hongwitayakorn)

### **Acknowledgements**

First, I would like to thank Michael J. Liebelt, my supervisor, for his help and support in everything. Without his excellent guidance and patience, my work definitely cannot be achievable.

All staff in the department of Electrical and Electronic Engineering, I appreciate their help for all these years since the first day I've been here. Thank you for everything.

I also want to thank my colleagues at Silpakorn University and my students out there for faith and belief that I can do this. In addition, a big thank to AusAID and Thai Royal Government for the scholarship.

And, of course, I'd like to thank all my teachers who gave me good knowledge from a very first day at school.

I have a very long list of friends and relatives who I want to thank. If I write it down, it would dominate the thesis. So, I would like to thank everyone with all my heart.

Last but definitely not least, I want to thank my mom, dad, sister, and brothers for everything. Also, I want to thank my wife who always be there for me and, at the time I wrote this, she is about to deliver the best gift I've ever got. It is the first child of us. What a marvelous timing! So, I can celebrate two things at the same time.

## Chapter 1

### Introduction

#### 1.1 Overview

The performance requirements of high performance computers are escalating tremendously in order to respond to the complexity of modern software applications. Much research has been conducted on techniques to improve the performance of microprocessors as they are deployed in almost every level of modern computers. The objective is to increase the number of instructions that can be executed per unit time. Researchers in the field of semiconductor technology propose to increase processor clock frequency, the reciprocal of time usage. Meanwhile, computer architects attempt to modify processor microarchitecture and improve compiler technology in order to execute multiple instructions simultaneously.

Instruction-level parallelism (ILP) is the dominant technique exploited in modern processor microarchitecture. Parallelism of incoming static sequential instructions is detected in order to execute multiple instructions concurrently. This technique can be implemented using both software and hardware approaches depending on the type of processor. VLIW (Very Long Instruction Word) and superscalar are two types of ILP processors [23], [29]. The former aggressively uses compiler techniques to obtain high levels of parallelism. Hardware techniques are used in the latter to capture incoming instructions and dynamically determine those that can be executed in parallel. Consequently, software applications can be run on superscalar processors without recompiling [12]. In this thesis, we focus on superscalar processors as they are the more common type and have been for many years.

#### 1.2 Superscalar Architecture

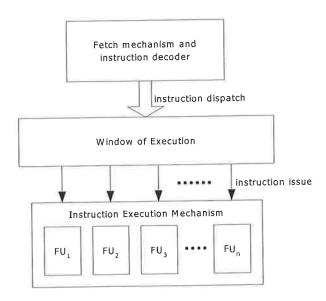

The operation cycle of a superscalar processor begins with fetching instructions from a static program into the processor using the *instruction fetching mechanism* and decoding them at the decoder unit. After this stage, the decoded instructions will be dispatched and temporarily accumulated in an instruction buffer called the *window of execution*. These instructions are no longer constrained by static program order. Therefore, they are free to be executed in parallel and ready to be issued simultaneously into the appropriate functional units located in the *instruction execution mechanism* after their operands become available, subject to data dependence and resource constraints [14], [15], [25], [32]. Figure 1.1 shows the diagram of superscalar architecture organization.

Figure 1.1 Organization of superscalar architecture.

To effectively exploit ILP is to improve superscalar processor performance by widening the window size for the purpose of increasing the possibility of finding data-independent instructions. More functional units are also required in order to be able to execute more instructions concurrently. Ideally, instruction-fetching bandwidth should correspond to the peak instruction dispatch and issue rate, to avoid the bottleneck problem [25]. However the constraint imposed by *control dependence* impedes the ability of the fetching mechanism to fetch instructions continuously, so it becomes important to overcome this constraint.

#### 1.3 Trace Cache Memory

The fetch unit must be able to feed a continuous stream of instructions to the window of execution as quickly as possible. It would be much easier if instructions were all lined up in contiguous fashion from start to finish. Unfortunately, such behavior is not found in typical application programs because they possess branch instructions. Branch instructions, the causes of control dependence, are very common in typical programs [8] and cause the instruction fetching mechanism to wait for branch outcomes to determine whether the branches are taken or not taken. In [1], the term *basic block* has been defined as an instruction group, which has one entry point and one exit point. Whenever a branch instruction is encountered, that will be the end of the basic block. Typically, the average run-length of a basic block is about 4 to 6 instructions [24]. Therefore, the sequentiality of instruction addressing is disrupted and the program is divided into numerous small basic blocks.

The branch prediction method was introduced to lessen the problem of control dependence by speculatively predicting the outcome of branches. However, there is a problem of non-contiguous location of individual basic blocks inside the conventional instruction cache. Basically, there are useless instructions lurking between useful basic blocks that are scattered among different cache lines, so a single fetch might not be so effective. *Trace cache memory* [24] is proposed not only to overcome this crucial drawback which blocks the possibility of fetching multiple basic blocks concurrently, but also to diminish the latency of fetching, which is the flaw of related prior research on high bandwidth fetching mechanisms. Moreover, the trace cache was designed to work outside the main pipeline of the processor. Therefore, it does not introduce an additional pipeline stage that would increase processing time.

Trace cache research has been conducted for very high performance microprocessors, i.e. 16 instruction-wide superscalar processors. Rotenberg et al [24] showed that the fetching performance of a processor using a trace cache is improved by 34% for integer benchmarks and 16% for floating-point benchmarks. Meanwhile, the trace cache work on enhanced features conducted by Patel [21] showed that a trace cache can outperform an aggressive instruction cache scheme by 14% of overall performance and increase the fetch bandwidth by 34%. Recently, Intel Corporation adopted trace cache technology for the Intel NetBurst micro-architecture in its mainstream commercial processor, the Pentium-4 [11].

There has been no reported study of trace cache performance for a small-scale microprocessor. Therefore, this research will study the effect of the different trace cache memory configurations for a VHDL model of a superscalar DLX machine [10], which can process only 2 instructions simultaneously. The design of the trace cache of the experiment will be done for two main configurations,  $TC_4$  and  $TC_8$  for 4 instruction-wide and 8 instruction-wide trace cache respectively. Each configuration is studied with a varying number of trace cache lines to understand the trade-offs between performance and cache size.

#### 1.4 Contribution of the Thesis

The contributions of this work can be summarized as follows:

- An analysis of the trade-offs between performance and trace cache size for narrow-issue sperscalar processor.

- An indication of whether trace caches are a worthwhile enhancement for narrow-issue superscalar DLX processor.

- A greater understanding of the performance characteristics of trace cache.

#### 1.5 Outline of the Thesis

The thesis is organized into 6 chapters. Chapter 2 describes the background of trace cache design and related research work. Details of the DLX architecture and the superscalar DLX model that have been used in this research will be presented in Chapter 3.

Chapter 4 explains the experimental setup and methods. The results of the experiment and corresponding analysis will be in Chapter 5. This chapter also includes the discussion of the experiment. Chapter 6 will be the conclusion of the thesis.

## Chapter 2

### **Background**

#### 2.1 Overview

Although the conventional instruction cache has served as a good source of instructions at high fetch rates for a long time, it cannot satisfy that high instruction consumption of wide issue processors. Instructions residing in the instruction cache are placed in compiled order and, unfortunately, typical programs possess many branch instructions. Consequently, several small basic blocks exist in run-time execution and disrupt the continuity of static instruction sequence in a wide instruction cache line. Even though the processors are designed to fetch several instructions in each line at the same time, many fetched instructions are abandoned. Therefore, fetching efficiency is low in this circumstance. To avoid this instruction supply bottleneck, the trace cache was introduced to increase effective instruction fetch bandwidth.

In a superscalar architecture, the sequences of executed instruction from the pipeline are dynamic and divided into several basic-blocks by control instructions (e.g. branches, return, and etc.). These are called instruction traces. Several such instructions grouped together look like a VLIW instruction format but formed in dynamic sequence. The trace cache counts on two important properties of dynamic sequences of instructions, i.e. temporal locality and branch behavior [24]. That is, the most recently used instructions are most likely to be reused in the near future and branches mostly bias to one direction. If these dynamic traces are collected in a special kind of cache memory, the performance of the fetch mechanism will possibly be increased. There will be no need to fetch several times from different lines of the

instruction cache to obtain an instruction sequence possibly spanning several non-contiguous basic blocks.

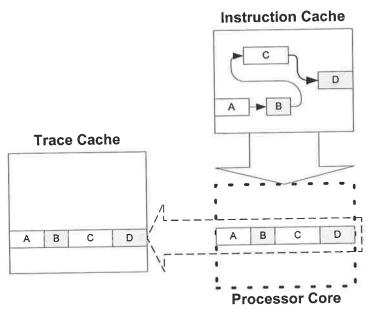

Figure 2.1 Trace cache overview

Figure 2.1 demonstrates the principle of the trace cache scheme. There are four basic blocks (A, B, C, and D) residing in non-contiguous locations in the instruction cache. They are logically connected together in run-time manner. Unfortunately, they are split in physical location due to static-compiled order; this is called "partial fetch" since each fetch could obtain just some part of all of the desired instructions. Time is wasted reading these instructions, as 3 cache reads are required (in this example). When these basic blocks are issued through the pipeline of the processor core they are rearranged in dynamic sequence or trace order (A, B, C, and D) to perform the task. This trace can be collected in the trace cache line. According to temporal locality and branch behavior as mentioned earlier, this trace is most likely to be used again in exactly the same sequence corresponding to the matching of fetch address and multiple predicted branches. Then, all instructions in this trace can be read in one fetch from the trace cache to the pipeline. This scheme obviously has the potential to increase fetching efficiency.

#### 2.2 Trace Cache Architecture

The trace cache architecture is composed of four main components:

- 1. the trace cache (trace container),

- 2. the fill unit,

- 3. the branch predictor, and

- 4. the instruction cache.

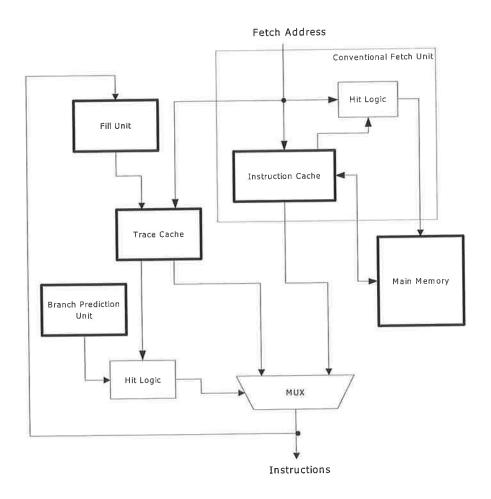

As shown in figure 2.2, instructions can be read from the instruction cache or the trace cache depending on the outcome of the *hit logic* which processes the incoming fetch address and the outcomes of the branch prediction unit. If it signals *hit* the trace cache will deliver instructions. Otherwise, instructions are supplied from the instruction cache. Instructions residing in the trace cache are collected by the fill unit, which copies instruction traces entering the processor execution pipeline.

Figure 2.2 Trace Cache Architecture Diagram

#### 2.2.1 The Trace Cache

The trace cache container is an array of fast-access memory, which dominates the area of the trace cache circuit. It collects several lines of trace issued from the fill unit. To each individual line of the trace cache is attached information similar to that in an ordinary instruction cache i.e. a *valid bit* to indicate availability of data in the line and a *tag* to identify the starting address of the trace. Moreover, there are some extended fields related to branch addresses because there might be more than one basic block inside the trace. All of this information is processed by the trace cache *hit logic* to determine whether an instruction fetch results in a trace cache hit or miss.

#### 2.2.2 The Fill Unit

The fill unit is an essential component of the trace cache organization as all of the instructions accommodated in the trace cache come from this section. It gathers dynamic instruction sequences from the processor pipeline, merges the incoming instructions with existing instructions to form a packet, provides the attached information for each trace cache line as described above, and sends the packet to a line of the trace cache container. The essential step in the formation of a trace packet is packet finalization. The maximum number of instructions n and the number of predicted branches m are the main trace-packet delimiters. Both Patel [21] and Rotenberg et al. [24] have built models which carry 16 instructions (n=16) with a maximum of three branch predictions (m=3). Then, four conditions for finalizing the trace-packet are:

- 1. the packet contains 16 instructions, or

- 2. the packet contains 3 conditional branches, or

- 3. the packet contains a single indirect jump, return, or trap instruction, or

- 4. incoming instructions could not be concatenated with the existing instructions since the sum would exceed 16 instructions.

#### 2.2.3 The Branch Predictor

The performance of any fetch mechanism relies on the precision of the branch predictor because an incorrect branch prediction causes a time penalty due to instruction recovery. In the case of a wide issue processor, a single branch predictor seems to be inadequate because a line of trace cache is likely to contain multiple basic

blocks, as mentioned earlier. Therefore, a trace in the trace cache would be more effective if the predictor can cover all of the branch instructions in a line and if the outcome of the prediction is sufficiently accurate. Otherwise, the penalty would be more severe and waste more time.

Unfortunately, at a present, the technology of multiple branch predictors is still immature and the accuracy is less than that of single branch predictors. However, the scheme known as two-level branch prediction [34] showed impressive prediction accuracy at 97%. This method can be implemented within the trace cache scheme to predict three branch outcomes in a single cycle.

#### 2.2.4 The Instruction Cache

Even though the trace cache plays an important role supplying instructions for the processor, the conventional instruction cache is still needed. When the *hit logic* signals a trace cache miss, the instruction cache has to provide the requested instructions, instead. Moreover, the instruction cache, itself, is the instruction gateway connected between main memory and the processor. However, the size of the instruction cache might be trimmed down to suit such less frequent activities.

#### 2.3 Related Work

There is a large amount of published research, using both hardware- and software-based approaches, on high bandwidth fetch mechanisms. Some hardware-based approaches are listed here for the purpose of tracing back the history of the trace cache. Some of these are currently adopted in parts of the trace cache scheme. The others are significant competitors of the trace cache approach.

#### 2.3.1 Trace Cache History

The history of trace cache development begins with the fill-unit, which was introduced as hardware proposed to increase the front-end performance of the VAX architecture. Melvin et al [16], showed that the parallelism of such a sophisticated instruction set architecture can be exploited by using a fill-unit to create large execution atomic units (EAUs) dynamically. Hypothetically, the larger EAUs contain more microoperations able to be executed simultaneously. Each EAU is stored in the

decoded instruction cache to be reused by the execution unit. In subsequent work [17], Melvin and Patt varied the size of EAUs of the dynamically scheduled machines using a fill-unit unit to gather two or more instruction basic blocks in the associated cache. The results showed that larger EAUs effectively enhance the performance of the processor because of the higher utilization of processor pipeline slots.

In 1994, Franklin and Smotherman [6] adopted the fill-unit for their multiple instruction issue architecture. The fill-unit dynamically packs multiple instructions into VLIW-type instructions and stores them in the *shadow cache*. When the instructions in a shadow cache line are required, they can be issued and executed simultaneously. The proposed fill-unit also includes logic for checking data dependencies of stored instructions as well as a unit for dealing with delayed branches. There is also a branch predictor to assist the fetching mechanism with speculative execution in order to create effective cache lines.

In 1994, Peleg and Weiser [22] patented their new instruction cache design, which is similar to the trace cache, namely the *Dynamic Flow Instruction Cache*. This scheme enhances the fetching mechanism for superscalar machines by storing 2 instruction basic blocks in a cache line. The branch instruction at the end of the first basic block has been predicted and the outcome of the prediction is the physical address of the first instruction of the following basic block of the cache line. Instructions in the cache are collected dynamically from the instruction flow and all instructions in a cache line can be fetched in a single access. The difference between this cache scheme and the current trace cache is that in the former each basic block is used as a starting point for each trace packet created.

The other trace cache lookalike is the *Expanded Parallel Instruction Cache* (*EPIC*) proposed by Johnson in 1994 [13]. This architecture has been designed to enhance in-order superscalar machines by reducing the complexity of the instruction decoding and issuing mechanism. Each line of the *Expansion Cache* contains decoded and dependency analyzed instructions, which were routed to certain execution units. Therefore, it can reduce the processing time once the instructions are fetched. The performance of this design is approximately equal to one of the more complex out-of-order superscalar machines with traditional instruction cache.

Rotenberg et al. [24] designed the trace cache scheme consisting of a small cache with a large instruction cache embedded in a 16-wide issue superscalar

cache design, fill unit design, and in particular, multiple branch prediction. They showed that a large trace cache assisted by a small instruction cache outperforms alternative configurations [24]. Therefore, the instruction cache can be designed less aggressively as it is subject to fewer instruction accesses. Patel et al. continued their work to improve the performance of the trace cache as reported in [18], [19], and [20]. They explored several enhancements to the trace cache model in order to overcome performance limitations. Recently, Patel assembled all of his previous works and some new features of the trace cache into his Ph.D. dissertation [21]. He describes and evaluates the basic trace cache fetch mechanism, which outperforms an aggressive instruction cache. High performance was achieved through the use of several enhancements including:

- Partial Matching the ability to pick up the useful blocks in a matching trace line and to discard the rest instead of wasting the whole trace due to branch prediction mismatch.

- Inactive Issue instead of totally discarding useless blocks because of branch prediction mismatch as in Partial Matching, Inactive Issue allows the whole trace to be fetched and marks these mismatch blocks as inactive blocks. There is no effect on fetching performance if branch prediction was correct. Otherwise, the inactive blocks would offer useful instructions to be executed.

- Branch Promotion in order to reduce the bandwidth of the branch predictor and increase the effectiveness of the fetch mechanism, Branch Promotion embeds the statically predicted information (taken/not taken) to strongly bias branch instructions [25].

- Trace Packing this enhancement sacrifices trace cache area in order to increase individual fetching capability within the loop as shown in figure 2.4. In case of a 16-instruction trace, segment AB already occupied 11 slots and left 5 slots for the next segment. Unfortunately, segment C has 6 instructions and can not fit in. Therefore, the possible traces would be AB, CA, and BC. Using Trace Packing will store 6 combinations for the dynamically unrolled loop as follows: A6B5C5, C1A6B5, C6A6B4, B1C6A6, B5C6A5, and A1B5C6. The subscripts denote the number of instructions in each particular segment.

Figure 2.4: A loop contains 3 segments.

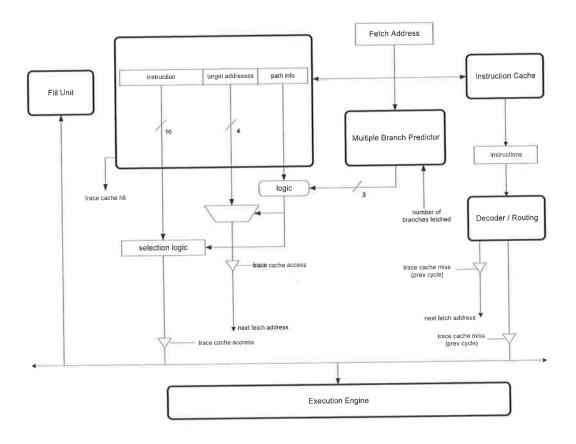

The aggregation of Partial Matching, Inactive Issue, Branch Promotion, and Trace Packing, make the trace cache outperform the state-of-the-art *Sequential-Block* instruction cache scheme both in processor performance (IPC metric) and in average fetch rate. Furthermore, Patel's analysis showed that as fetch rate increases, branch resolution time increases. Lastly, a next-generation processor implementation is described which achieves high fetch rates at high branch prediction accuracy. Figure 2.5 shows this trace cache fetch mechanism.

Figure 2.5: The trace cache fetch mechanism [19]

Comparing figures 2.3 and 2.5, even though they are both based on the trace cache fetch mechanism, there are some differences between them affecting overall performance. The former model delivers dynamic instruction streams that have been captured before they are sent to the decoder. On the other hand, in the latter model decoded instructions are sent to the fill unit before being dispatched to the execution engine. Therefore, when a trace cache *hit* is signaled, instructions go directly through the execution engine without passing to the decoder/routing again. Furthermore, these instructions are already analyzed for dependencies and pre-routed to appropriate execution units. The other difference between the models is the information contained in each trace cache line. The latter model includes not only the branch target address for checking trace cache hit/miss, but also path information which facilitates the path enhancement of the model i.e. Partial Matching and Inactive Issue.

#### 2.3.2 Other High Bandwidth Fetch Mechanisms

The *Branch Address Cache* [34] and *Collapsing Buffer* [4] have been previously mentioned as multiple basic block fetch mechanisms. They achieve high effective fetch rate, although they cannot perform as well as a trace cache. However, it is worthwhile to examine them to see why this is so.

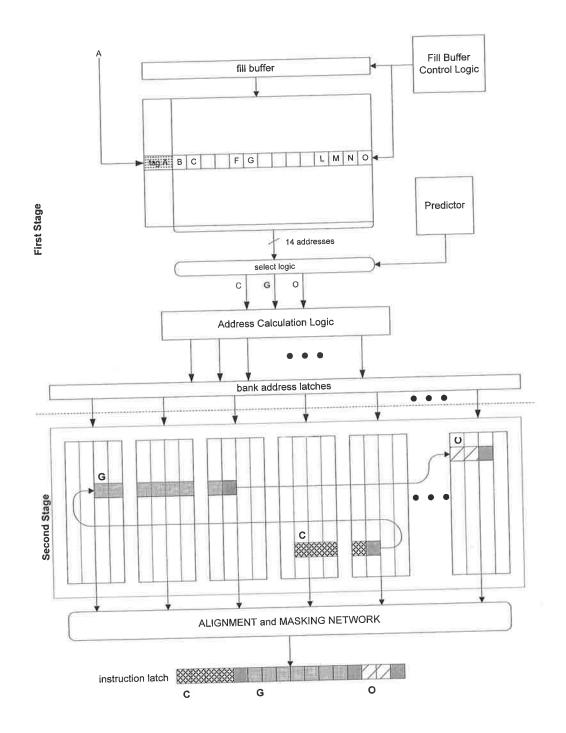

In 1993, Yeh et al. proposed the branch address cache scheme [34] shown in figure 2.6. It generates multiple fetch addresses in a single cycle resulting from the branch address cache working together with the branch predictor. These addresses will be calculated as indices to point to the exact location of each basic block residing in the interleaved instruction cache. Finally, all targeted instructions are passed through the alignment and masking network in order to form a packet ready for issue. The problems of this scheme are hardware complexity and its lack of amenability to aggressive branch prediction.

Figure 2.6: The Branch Address Cache.

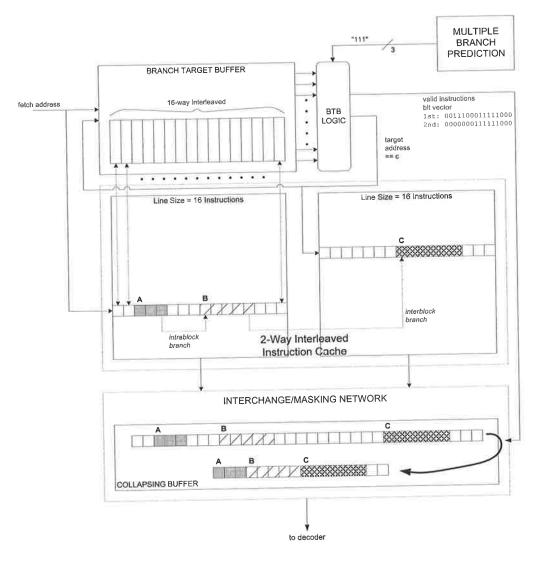

Conte et al. proposed the Collapsing Buffer [4] as shown in figure 2.7. Two nonadjacent cache lines can be fetched together since the scheme uses two passes through an interleaved branch target buffer. Each pass through the branch target buffer produces a fetch address. Moreover, the BTB can detect any number of branches in a cache line. Therefore, it can detect intrablock branches and eliminate the

unused instructions by using the collapsing buffer in the interchange/masking network. Likewise, this approach adds more process stages to the fetching pipeline and this decreases overall performance.

Figure 2.7: Collapsing Buffer

#### 2.4 Conclusion

In summary, the trace cache mechanism can perform better than other aggressive approaches in respect of fetching ability but it needs sophisticated logic to create effective traces and a substantial memory area. Therefore, a trace cache might not be cost-effective for general-purpose processors at the present. However, the previous trace cache studies have been conducted only on wide-issue processors.

Hence, this research focuses on the effectiveness of trace cache on narrow-issue processors. The objective is to find out the significance and trade-offs of TC parameters that affect the performance of the cache scheme and the usage of cache space for the consideration in TC implementation on narrow-issue processors.

## Chapter 3

## **Experimental Processor Model**

#### 3.1 Overview

The trace cache experiments in this thesis are based on simulation. A superscalar implementation of the DLX architecture has been chosen as the experimental processor model. The VHDL language is used to describe the simulation model, since the language facilitates both model construction and testbench simulation. In addition, the working model could be used as a foundation to synthesize the processor using suitable VHDL synthesis tools. Fortunately, there is a superscalar DLX processor model [10] in VHDL that is suitable for the proposed experimentation.

#### 3.2 DLX Architecture Summary

The DLX architecture was first introduced by Hennessy and Patterson [9]. It possesses features, which can be commonly found in several successful processors based on the RISC philosophy.

The significant features of the DLX architecture are

- an uncomplicated load/store instruction set,

- pipelining effectiveness,

- an easily decoded fixed-length instruction set, and

- efficient machine code, as targeted from high-level program compilation.

#### 3.2.1 DLX Registers

There are three register types in the DLX architecture. Firstly, the general-purpose registers (GPRs) comprise thirty-two 32-bit registers named R0, R1, ..., R31. The value of R0 is permanently set to zero. The GPRs are used for all integer operations and memory addressing modes. Secondly, the floating-point registers (FPRs) comprise thirty-two 32 bit single-precision floating point registers named F0, F1, ..., F31. They can be used as double-precision floating point registers (64-bit) by coupling odd and even registers into a register pair (F0, F2, ..., F30). These registers are used only for floating-point operations. Lastly, the special-purpose registers comprise several registers for purposes such as masks and flags.

#### 3.2.2 DLX Data Types

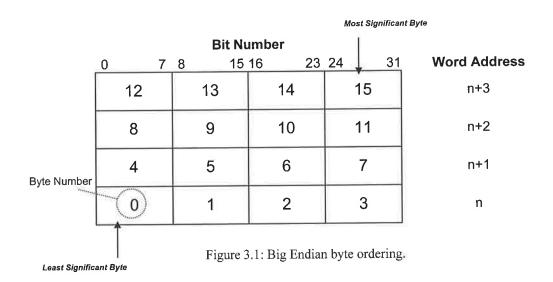

There are 8-bit (byte), 16-bit (half word), and 32-bit (word) integer data plus 32-bit single precision and 64-bit double precision floating point data type. They conform to Big Endian byte ordering as illustrated in figure 3.1.

#### 3.2.3 DLX Addressing Modes

The explicitly supported data-addressing modes in the DLX are immediate and displacement, using 16-bit fields as immediate data and displacement address fields, respectively. However, putting 0 in the 16-bit displacement field can accomplish the register-deferred mode and using register R0 as a base register associated with 16-bit field can accomplish absolute addressing. Therefore, there are four effective addressing modes available in the DLX.

#### 3.2.4 DLX Instruction Types

There are three different instruction types: I-type (immediate), R-type (register), and J-type (jump). All instructions are 32-bit format as shown in figure 3.2.

#### a) I-type instruction immediate rd Opcode rs1 16 5 5 6 b) R-type instruction function rd rs2 rs1 Opcode 11 5 5 5 6 c) J-type instruction Offset added to PC Opcode 6 26

Figure 3.2 DLX instruction format.

Since all instructions are of fixed-length format, instruction decoding is very simple.

DLX is an easy architecture to understand and, moreover, widely studied and modeled. Consequently, it is a useful processor on which to base the study of the trace cache.

#### 3.3 The Superscalar DLX Model

The superscalar DLX model used in this research was created by Horch in the VHDL language [10]. Both the source-code and documentation are provided at URL <a href="http://www.rs.e-technik.tu-darmstadt.de/TUD/res/dlxdocu/SuperscalarDLX.htm">http://www.rs.e-technik.tu-darmstadt.de/TUD/res/dlxdocu/SuperscalarDLX.htm</a>. Although the documents were written in German, the source-code is commented in English and is quite simple to follow. Figure 3.3 shows the structure of the superscalar DLX processor.

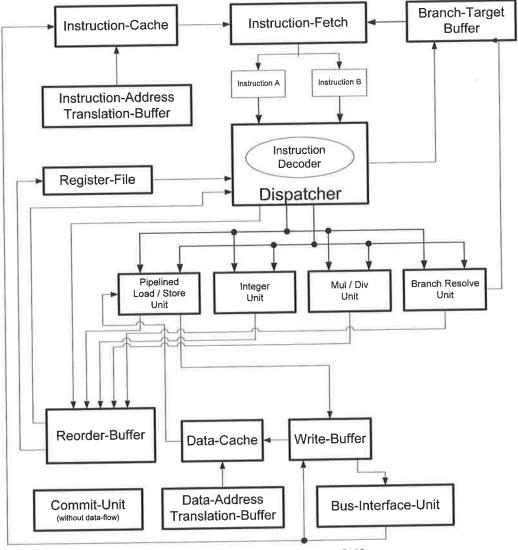

Figure 3.3: Superscalar DLX structure. [10]

The microarchitecture of this model is a pipelined superscalar processor. It can fetch a maximum of two instructions simultaneously in a single cycle. The instruction fetch unit is supported by a 64-byte instruction cache coupled with a 4 entry instruction address translation buffer (ITB). There is a branch target buffer (BTB) to provide the speculative target of branch instructions.

The dispatcher is the heart of the processor since it connects to every major unit of the model. Accordingly, it generates control signals to manipulate all processor activity from instruction entry until instruction commit. Moreover, the dispatcher also manages precise exception processing. This is assisted by the reorder-buffer, which works with the commit unit to commit instructions in program order.

There are four execution units, each with a reservation station: pipelined loadstore unit, integer unit (arithmetic logic unit or ALU), multiply-divide unit (MDU), and branch resolve unit. The load-store unit works cooperatively with the write buffer and 64-byte data cache equipped with 4-entry data address translation buffer (DTB). The ALU executes all logical, shift, and set-on-comparison instructions. Moreover, it mainly does the integer arithmetic calculation for addition and subtraction.

Integer multiplication and division can be performed by the MDU but the implementation of MDU is slightly different from the original DLX architecture. In the original architecture, multiply and divide instructions can be performed only with floating-point registers (F0-F31). Therefore, data type conversion instructions from integer to floating-point and vice versa (i.e. MOVI2FP and MOVFP2I) are available to enable integer multiplication and division using the floating-point multiply/divide unit. To avoid any implementation of floating-point operations, Horch defined a unique register file that can be addressed as GPRs (R0-R31) or FPRs (F0-F31). R0 and F0 are the same physical register and so on. Consequently, multiply and divide instructions (MULT, MULTU, DIV, and DIVU) perform integer multiplication and division on the GPRs. This variation from the standard architecture required some code modification, which will be described in chapter 4.

Lastly, the branch resolve unit determines actual branch outcomes, determines the target address to insert in the BTB and also indicates when a branch misprediction has occurred.

#### 3.4 The Fetch Unit

The fetch unit is the part that is of most interest in this research, since the trace cache is intended to improve the fetching performance beyond the conventional instruction cache. So, the original fetch unit will be described in detail, to provide information on the original model design.

The fetch unit has been designed to fetch a maximum of two instructions from the instruction cache in a single cycle if the address of the first instruction in the program counter is double word aligned. Word order within double word is Big Endian (i.e. 0x000000000 is the high word and 0x000000004 is the low word). The registers for storing the fetched instructions are divided into the stage A register and the stage B register. Both of them can store either high word or low word. Normally, stage A stores the high word and stage B stores the low word. However, stage A can

store the low word in which case stage B will become invalid. In the case of fetching two instructions when the address is double word aligned, but when stage A is not available, stage B can store the low word and the program counter will be increased by 4 bytes.

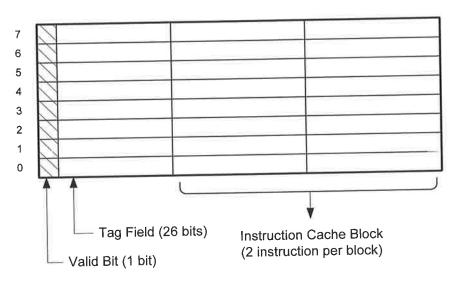

As mentioned above, there are two main units associated with the fetch unit. They are the instruction cache and the branch-target-buffer (BTB). The instruction cache in the original model has a small capacity and is configured as a direct mapped cache. It has 8 lines containing two instructions each. So, it can contain only 16 instructions (16\*4 = 64 bytes) at a time. The availability of instructions in each cache

Figure 3.4: Instruction cache structure.

block is indicated by the valid bit and the tag field used for address matching.

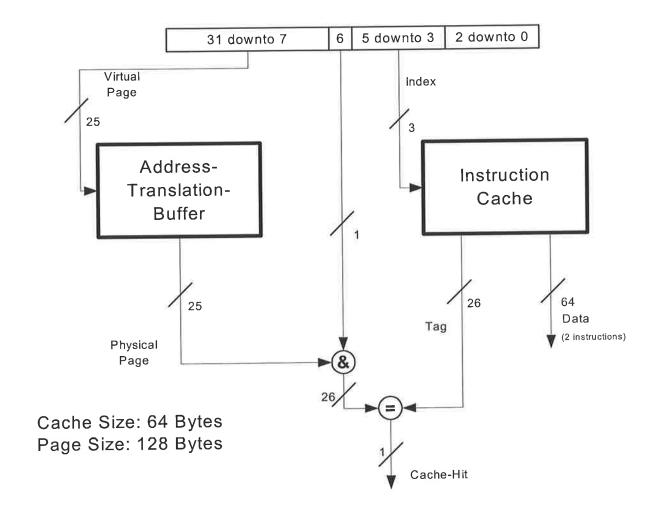

The instruction cache cooperates with the instruction-address-translation buffer (ITB) to convert a virtual page number (bits 31 to 7 of the program counter) into a physical page number and this is joined with bit 6 of the program counter. The results are used to compare with the tags of instruction blocks to determine cache hit or miss. The ITB has a 128-byte page size. Figure 3.5 shows the address translation mechanism of the instruction cache and instruction-address-translation buffer. This configuration is also used for accessing the data cache in this model.

Figure 3.5: Address-translation and cache-access. [10]

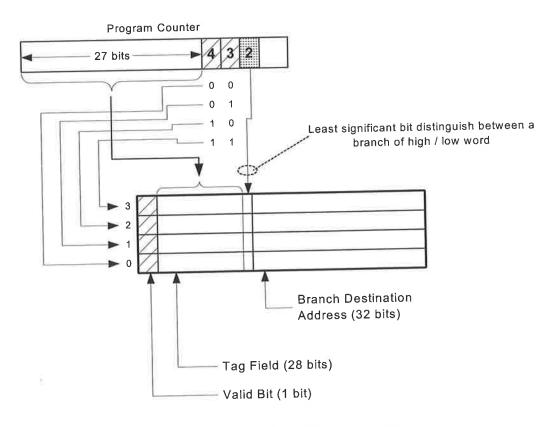

The branch-target-buffer (BTB) is a memory that contains destination addresses of previously executed branch instructions. These addresses are most likely to be the target of future branches. When one of these branches is fetched again, the BTB will speculate the direction of the next instructions without waiting for the outcome of branch condition determination. In this model, there are four slots within the BTB to store destination addresses. Like the instruction cache, each entry composes of a *valid bit* for indicating the availability of the BTB data and a *tag field* for address matching.

Figure 3.6: Branch-target-buffer structure.

Indexing to the BTB slot uses bits 4 and 3 of program counter (2 bits = 4 combinations). Then, the last three bits make all entries represent 8-byte aligned addresses. Consequently, the destination address stored in each slot has to indicate whether the branch is a high-word or low-word instruction. This is accomplished by attaching the extra bit as the least significant bit of the 28-bit tag portion. The extra bit comes from bit 2 of the program counter.

#### 3.5 Conclusion

The superscalar DLX model [10] is a narrow-issue processor model, which was written in VHDL format. It can execute integer programs including integer multiply and divide instructions without conversion between floating-point and integer data type. The implementation details of a trace cache on this processor model are described in the next chapter.

# Chapter 4

## **Experimental Setup**

This research was conducted to find out whether and how a trace cache memory can help a narrow issue superscalar processor to fetch instructions. As mentioned in chapter 3, an existing superscalar DLX processor model [10] was chosen to avoid spending the time required to build the processor from a scratch and give more time to focus on the trace cache model which is the target of this research. This chapter contains the explanation of an experimental setup that was used to implement the trace cache and to gain results for experimental analysis.

### 4.1 Trace Cache in the Superscalar DLX Processor

The trace cache is a source of instructions containing dynamic traces of instructions instead of static ones as an ordinary instruction cache does. Therefore, the trace cache is supposed to be an alternative repository, to compete with the embedded instruction cache to supply instructions to the execution unit.

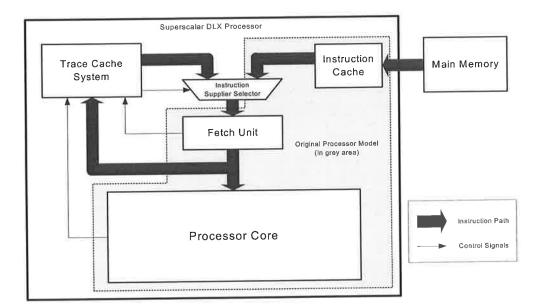

Figure 4.1: Trace cache placement in the superscalar DLX machine.

Figure 4.1 shows the placement of a trace cache in a way that would fit in with the original superscalar DLX processor model. The task of the trace cache is to collect instructions from the fetch unit and pack these into traces with help from control signals of the fetch unit itself and other units in the processor core, which determine how to pack them. The trace cache can feed these traces back to the fetch unit. However, the existing instruction cache is still the main supplier but also is the competitor of the trace cache. Therefore, the trace cache system must be equipped with trace cache 'hit' logic to make a decision on which instruction supplier would do the job.

It is possible to build a trace cache by gathering instructions from the main processor pipeline and producing instruction traces. However, incorporation of a trace cache would add a lot of complexity due to the original processor model, which was not designed for this kind of expansion. Hence, the other way to accomplish this mission is to leave the original superscalar DLX model untouched and examine the utilization of the trace cache passively. In the other words, we build the whole trace cache mechanism and investigate whether instructions collected in the trace cache match the current fetched address in the program counter register of the processor.

This allows us to determine the effectiveness of the trace cache by measuring trace cache hit rate, but we do not provide instructions from the trace cache to the processor core since we are not attempting to measure the overall performance

increase due to the trace cache. In other words, we will assess trace cache performance in terms of trace cache hit rate and not be concerned with processor performance improvement due to the higher fetch rate produced by the trace cache. The latter is highly dependent on implementation technology.

# 4.2 Trace Cache Line Size

In prior trace cache models [21,24], the superscalar processor models have wide instruction-paths, which are significantly different from the modest 2-instruction-wide superscalar DLX machine we use in this research. In this circumstance, the trace cache model used in this experiment is likely to be quite different from them.

On a 16-instruction-wide superscalar processor, the individual trace cache line is designed to fit 16 instructions and is able to feed a maximum of 16 instructions simultaneously to the fetch unit. This approach would not fit with the 2-instruction-wide processor (i.e. making the trace cache to accommodate just only 2 instructions in a cache line) because the average basic block for typical applications is about 4 to 6 instructions [24]. More importantly, the significant idea of the trace cache system is to provide a trace that covers the basic block and to overcome the penalty of branch misprediction. In this circumstance, we will provide a trace cache line size of 4-instruction-wide or 8-instruction-wide to cover at least one basic block. The reason for making 2 versions of trace cache line size is to find out an appropriate configuration from the experiment results. In this project, we call the 4-instruction-wide model  $TC_4$  and  $TC_8$ , respectively.

# 4.3 Trace Cache Model Components

There are 4 main parts that work in concert, starting from gathering instructions from the fetch unit until determining a trace cache 'hit' or 'miss'.

# 4.3.1 Instruction Gathering Unit

This unit works closely with the fetch unit. In the original processor model, the fetch unit provides two registers for holding fetched instructions. Both instructions

could be dispatched through the execution windows simultaneously or just one of them depending on the availability schedule of the required execution unit for each instruction. The instruction that was left behind will be fed in the next clock period in which the functional unit is available. To avoid double copying of the same instruction from different fetch cycles, the instruction-gathering unit must be able to determine how many instructions could be collected and which one of them should be collected in the case that only one instruction could be dispatched. The determination can be made by consulting a group of control signals. These signals are created by the dispatcher in which they are originally used for checking the validity of incoming instructions at the fetch stage. After the determination is accomplished, the individual valid instruction is ready to be placed into the appropriate position of the fill-buffer under the fill-policy for creating a dynamic instruction trace.

#### 4.3.2 Fill-Buffer

This buffer is a temporary memory which stores valid incoming instructions as traces, before transferring them to the trace cache memory space. However, it is the most significant part of the mechanism because the usability of packed traces depends directly on the fill-policy that crafts the individual trace. Because of the different trace cache line size and different number of basic block coverage, the fill-policy will be different from the previous trace cache works in [21] and [24]. Details of fill-policy will be described in section 4.3.2.2 Fill-Logic and Fill-Policy.

#### 4.3.2.1 Fill-Buffer Configuration

The buffer comprises two main sections, *Trace Content* and *Trace Information*. *Trace Content* stores collected instructions and their addresses. Meanwhile, *Trace Information* stores information associated with the trace which is used during fill-buffer to trace cache transfers. *Trace Content* is constructed as 4 lines (line numbers 0-3) by the number of instructions (4 and 8 instruction slots for *TC\_4* and *TC\_8*, respectively.) Figure 4.2 shows the structure of the fill-buffer.

- **Branch Existing Flag:** This flag indicates whether or not there is a branch instruction in the buffer line.

- **Branch Position:** Together with the previous flag, this field pinpoints the location of the available branch instruction of the line.

The bit-length of the information fields *Trace Size* and *Branch Position* depend on trace cache line size. Each of them is 2 bits for  $TC_4$  and 3 bits for  $TC_8$ . Note that, as explained in the following section, each trace cache line will contain no more than one conditional branch (i.e. 2 basic blocks).

#### 4.3.2.2 Fill-Logic and Fill-Policy

The most significant part of the whole fill-buffer is the fill-logic, which determines how to fill instructions into the buffer, because the usefulness of traces directly depends on the characteristic of the traces themselves. The implementation of the fill-logic is ruled by the fill-policy, which defines how to construct and when to terminate a trace from instructions collected from the instruction gathering unit.

The collected instructions will be put into available slots one after another in the current incomplete trace until the trace is terminated by one of the following conditions:

- 1. when the size of the current trace including one or both of the new incoming instructions equals the buffer line size, or

- 2. when either one of the new incoming instructions is an unconditional branch (jump), RFE, or trap, or

- 3. when the current trace already possesses a conditional branch and either one of the new incoming instructions is also a conditional branch. It was decided that there must be maximum of 2 basic blocks per line because general programs have basic block run-length about 4-6 instructions [24]. Hence, the narrow cache width like  $TC_4$  and  $TC_8$  will rarely be able to accommodate more than 2 basic blocks.

Accordingly, the fill-logic fundamentally composes of a set of pointers used to locate the current row and slot in the trace content space of the fill-buffer for each of the incoming instructions and their addresses. The most important task of this unit is to manipulate the pointers to implement the above rules correctly.

Rule 1 is the simplest way of terminating the line, when an incoming instruction makes the current trace reach the limit of the buffer line size. Note that there might be either one or two instructions collected from the fetch unit. In case there is only one instruction, if the length of the incomplete current line plus this instruction equals the buffer line size, the instruction will be placed into the line and also terminates this line. Meanwhile, the pointers will be updated to the beginning of the next line. However, if there are 2 incoming instructions, there could be two distinct cases.

- Case 1: The first incoming instruction of the two occupies the last slot of the current buffer line. Therefore, this line will be terminated and the other instruction will be placed in the beginning slot of the next line.

- Case 2: There are two slots left in the current line while there also are 2 incoming instructions. The logic can place both instructions into the slots, terminate the current line, and start the next line for the next incoming instructions.

If the trace was terminated by rule 1, it means that the line was fully occupied by instructions that are most likely coming from the same basic block and they can be put in the buffer very easily in practice. This scenario is quite rare in reality because there are many instructions that break into several small basic blocks [24]. Therefore, rule 2 and rule 3 are often the ones that terminate the trace.

Rule 2 and rule 3 handle instruction-path changing instructions (i.e. unconditional branches, RFE, and traps) and conditional branches, respectively. Therefore, it is necessary to enable the fill-buffer to classify instruction types. If the former was detected in either one of the incoming instructions, rule 2 will be applied. Basically, that instruction will be put in the current position provided by the pointers and then the line will be terminated immediately.

According to the structure of the fill-buffer (see figure 3.3), there are 2 fields in the trace information concerning branch instructions. The 'branch existing flag' indicates whether or not there is a branch existing in the line yet. This field will be set once a conditional branch instruction was inserted in the line. If the flag is set and if one of the incoming instructions was detected as a conditional branch, the logic will push that branch to start in the new line next to the current line even though there is a space left to fit that instruction.

Apart from manipulating pointers to place instructions into their places by applying the fill policy rules, the fill-logic also has to complete the trace information of each buffer line. However, this task has to be done in parallel with the pointer manipulation.

- The 'buffer line ready' flag is set immediately after the current line was terminated.

- The 'trace size' field is the counter that counts the number of instructions placed in the buffer line continuously until the line is terminated. Once the line was terminated, this field can tell how many instructions are in the particular buffer line.

- The 'branch instruction flag' was mentioned above.

- The 'branch position' indicates the location of the branch instruction within the trace. This field is updated once the branch instruction was placed in the buffer line. This information can be extracted from the pointers that locate the position of the instruction.

#### **4.3.3 Trace Cache Memory**

#### 4.3.3.1 Trace cache memory structure

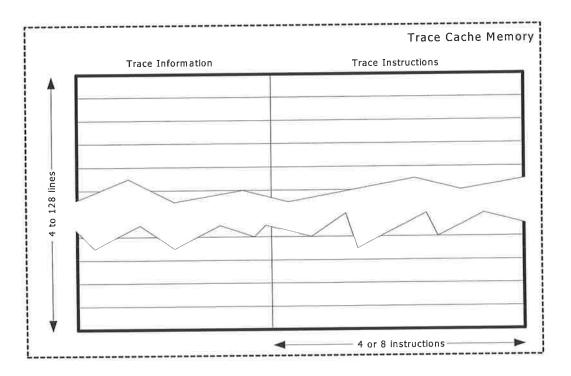

Figure 4.4: Trace cache memory structure.

The structure of the trace cache memory is quite similar to that of the fill-buffer. Figure 4.4 shows the structure of the trace cache memory space. There are also 2 sections: *Trace Information* and *Trace Instructions*.

- Trace Instructions stores only sequences of instructions since it is not necessary to store instruction addresses anymore. However, significant instruction addresses of the trace (i.e. the address of the first instruction and the address of the branch target instruction (if any) of the trace) are kept and appear as tags, which will be stored in the trace information portion.

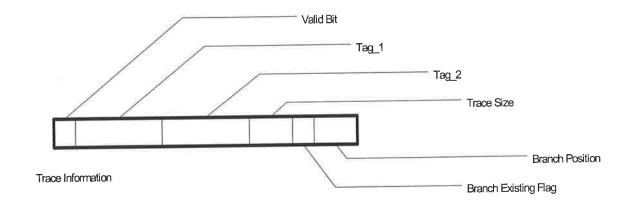

- Trace Information comprises 6 information fields.

Figure 4.5: Trace Information portion of the trace cache memory.

- Valid bit: This is a flag to indicate whether or not the particular trace cache line is occupied by valid cache content.

- Tag 1: This is the tag field of the first instruction in the line.

- Tag\_2: This is the tag field of the branch destination instruction address if there is a branch instruction available in the line. Otherwise, this field is an identical copy of tag\_1.

- Trace Size.

- Branch Existing Flag.

- Branch Position.

The last three fields of trace information are identical copies of 'trace size', 'branch existing flag', and 'branch position' fields of the associated fill-buffer entry as described in section 4.3.2.1 Fill-Buffer Configuration.

In this experiment, the number of trace cache memory lines is one of the interesting parameters to investigate. It ranges from 4 up to 512 cache lines (increasing by factor of 2) to analyze the effect of trace cache memory size on the trace cache utilization. This parameter will be varied for both  $TC_4$  and  $TC_8$  configuration.

#### 4.3.3.2 Buffer-cache transfer

Every clock cycle, there must be a procedure to check whether there are any traces ready in the fill-buffer waiting to be transferred into the trace cache memory space. The buffer-cache transfer unit was built to accomplish this task. Moreover, the unit has to make a decision whether the new trace should be placed into the trace cache memory or dropped out.

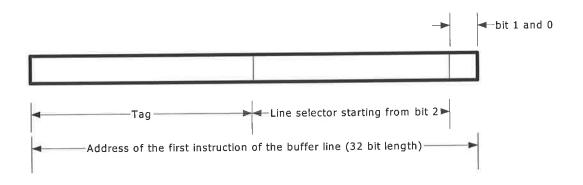

#### □ Trace cache memory line selection

When there is a ready fill-buffer line, the address of the first instruction of the buffer line will be used as the trace cache memory line selector. Based on a direct mapped cache, the number of extracted bits used for line selection depends on the number of lines of trace cache memory (i.e. 2, 3, 4, 5, 6, and 7 bits are for 4, 8, 16, 32, 64, and 128 lines, respectively). The position of the extracted bits starts from the third bit of the address (see figure 4.6).

Figure 4.6: Trace cache line selector is extracted starting from bit 3 of the address word.

#### □ Commencing the transfer

Once the destination line was decoded, the transfer would be commenced if:

- There is more than one instruction in the ready-to-transfer fill-buffer line. This avoids single-instruction traces, which are not likely to be very useful, from occupying an entire TC line.

- The trace size of the ready-to-transfer fill-buffer line is longer than the existing trace in the selected memory line. Hypothetically, a longer trace provides more instructions and this would increase the probability of finding more useful instructions.

#### □ The contents to transfer

The contents from the fill-buffer line are:

- All instructions in the trace (note: addresses of these instructions will be abandoned).

- The extract (Bits 31 to 2) of the address of the first instruction and the address of the branch instruction destination (if any) to fit in 'Tag\_1' and 'Tag\_2' of the cache line.

- Identical copies of 'Trace size', 'Branch Existing Flag', and 'Branch Position' from the buffer line for each field with the same name of the cache line.

# □ Finishing the transfer

After the transfer was complete, there are 2 tasks to be done.

- Reset all fields in the buffer line to make it ready to accommodate a new trace.

- Set the 'Valid Bit' of the selected cache line to signal the validity of the content.

# 4.3.4 Trace Cache Hit Logic

As mentioned earlier, the original DLX model will be left untouched and the performance measurement will be done passively. The trace cache hit logic is the unit assigned to find out whether the instruction at the current address in the program counter register and its successors can be found in the trace cache. Therefore, this function is the point at which can be made the measurement of trace cache hit rate.

The typical instruction-cache 'hit' is the outcome of comparison between the value in the program counter register of the processor and the tag of the selected line. This is the valid hit although the required instruction is not necessarily the first

instruction of the line since its tag covers all of the instructions of the selected line. This is different from the trace cache 'hit' definition, particularly, the trace cache configuration of this experiment.

## □ Trace cache information for 'hit' or 'miss'

The trace cache is supposed to collect instructions from the dynamic instruction stream. Although a trace cache line has a fixed size line into which instructions are placed, we can not forecast which instruction would be the first instruction of the cache line and how many instructions it can collect for a trace. Moreover, some traces may contain a branch instruction with a destination instruction whose address is not in consecutive order. Consequently, it is not possible to make the tag address cover all of the instructions in a trace cache line. In addition, the execution-path of the processor is only 2 instructions-wide. Then, all instructions from the selected trace cache line can not flow through the instruction-path simultaneously like those in the original instruction cache. One trace cache line might contain instructions to be fed through the instruction-path in several successive cycles. Therefore, the trace cache 'hit' or 'miss' depends on the corresponding trace information and the trace information must be able to indicate:

- how many instructions there are in a particular trace,

- the address of those instructions,

- whether the trace possesses a branch,

- the direction (taken / not taken) of that branch instruction.

## □ Trace cache 'hit' or 'miss' determination

There are 2 types of trace cache 'hit': a hit on the first instruction of the cache line and a hit on the rest of the line. The former can be detected by matching the current value in the program counter (PC) with the 'tag\_1' of the selected cache line. After a hit on the first instruction, it is possible to have a hit on the rest of the line in the next fetch. Thus, there must be a line-hit flag to indicate that the first instruction of that line has been hit. This method will enable the hit logic to check out the rest instructions.

- 2. Add the run time startup code crt0.0 to the start of the compiler output.

- 3. Run this file through the standard link editor, ld.

- 4. Edit the *a.out* file to set the load addresses for the text and data segments, as required by the simulation model.

- 5. Use the perl script to transform the floating-point instructions.

- 6. Edit the file to add nops around the jr instructions.

- 7. Assemble the resulting file ("dlx.asm") into object code ("dlx.out") using dlxasm.

The crt0.0 file and perl script are listed in Appendix D and are included in the companion CD-ROM.

At the end, the assembly codes were assembled into binary code as .out file for the processor simulation. The assembler named dlxasm (downloaded from http://www.ashenden.com.au/designers-guide/DG-DLX-material.html).

# 4.5 Simulation Testbench Configuration

The testbench configuration for simulating the superscalar DLX processor model has been set to run DLX binary-assembled files. A program used to run on the simulation must be named as 'dlx.out' and fit within 32 kilobytes memory range (0x0000 to 0x7FFF). Originally, the capacity of the main memory was only 16 kilobytes but this was expanded to accommodate larger test programs. Note that there must not be floating-point instructions in the test programs due to the processor design. The output file will be created as 'dlx.dump' if it was programmed to generate outputs.

# 4.6 Measuring the Trace Cache

In order to analyse the performance of the trace cache, the number of TC hits and misses were collected. Hit and miss counts of the original instruction cache and also the total cache accesses were also required for referencing purposes. The final sum of trace cache hits and misses from the trace cache lines is too coarse a metric to make any detailed analysis, therefore, the activities of each line of trace cache memory were recorded as described in the Appendix A.

In addition, there must also be analysis of the cache space usage because the trace cache model occupies real estate on the chip once it is implemented.

#### 4.7 Conclusion

This research project benefits from the use of an existing processor model in that it was not necessary to set up the experiment from scratch. However, this model constrains the implementation of the original processor and the ability to expand the instruction cache. This chapter has described the way in which the trace cache was constructed and the method used to measure the trace cache performance in the aspects of usefulness relative to the instruction-cache and space usage. VHDL source code is included in Appendix B.

# Chapter 5

# **Results**

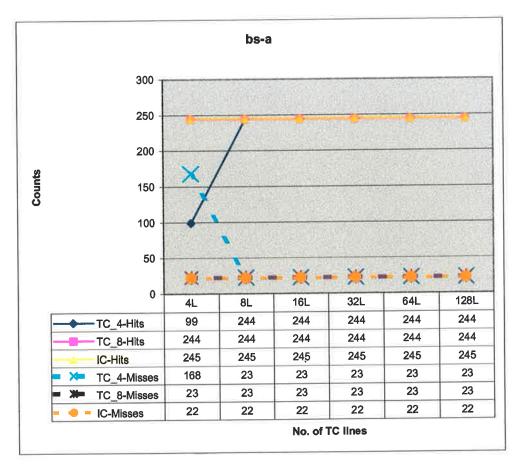

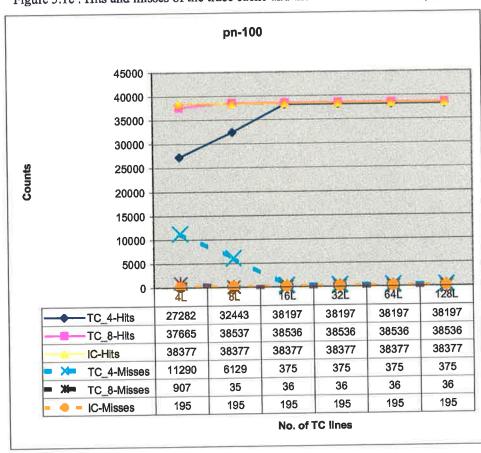

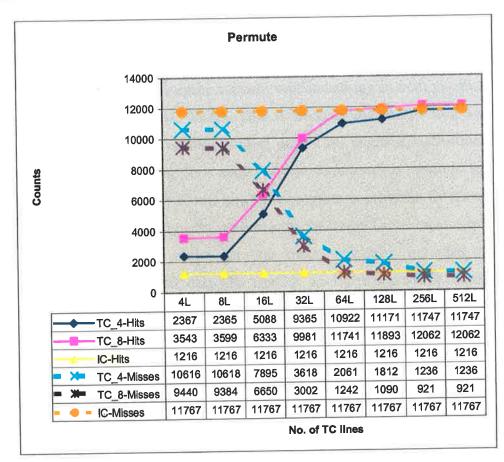

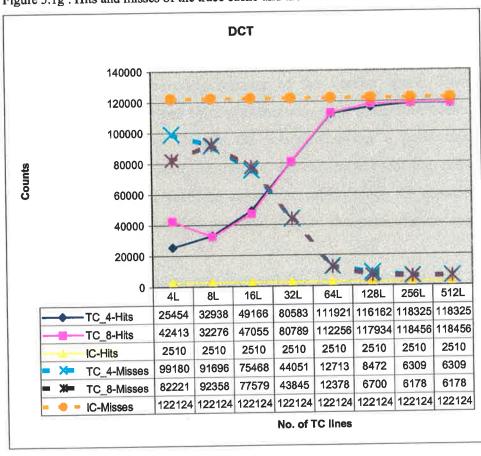

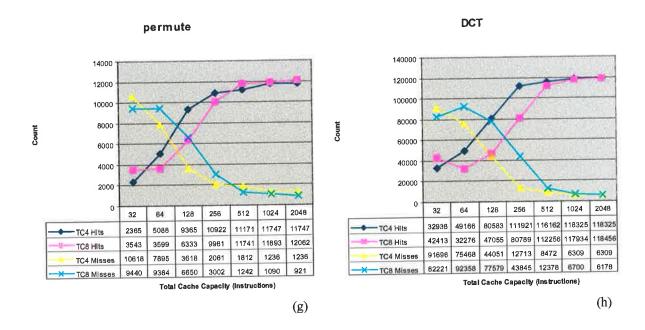

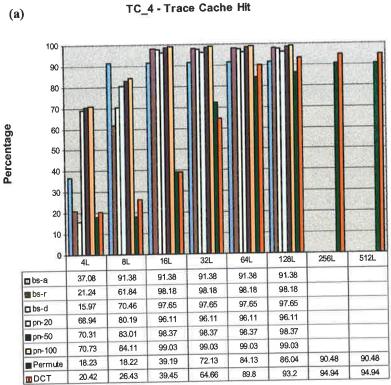

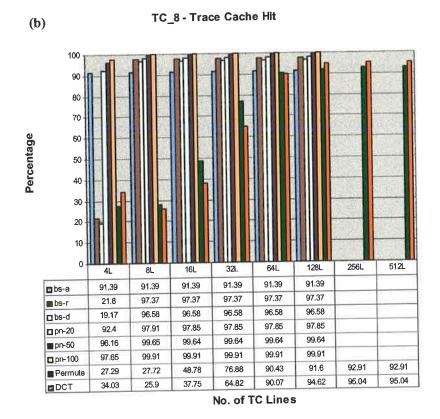

The trace cache was simulated in two configurations: a 4-instruction wide  $(TC_4)$  and an 8-instruction wide  $(TC_8)$  trace cache. In each case the number of trace cache lines was varied from 4 to 512. We will use 4L, 8L, and so on to denote individual cache line configurations. Each one of them will be simulated on 4 different test programs: bubblesort (bs-a, bs-r, and bs-d), primenumber (pn-20, pn-50, and pn-100), permutation, and DCT. For bubblesort and primenumber, the simulations were performed for 4L to 128L only, because trace cache performance became steady before reaching 128L and certainly would not vary for 256L and 512L configurations.

#### 5.1 Overview

This experiment is meant to determine the effect of a trace cache on a narrow-issue processor like the Superscalar DLX in order to be able to determine whether the trace cache is worth considering for implementation on this kind of microprocessor. Obviously, performance comparison between the trace cache and the originally embedded instruction cache seems to be inevitable. Unlike the trace cache, however, it proved to be impractical to increase the capacity of the instruction cache in order to make a fair comparison between the two. For this reason the instruction cache capacity was not varied in these studies. The instruction cache can hold a maximum of 16 instructions when the trace cache can increase virtually unlimited. The best case for fair comparison would be  $TC_4$  at 4 lines of trace cache, in which the total capacity of the cache is 16 instructions ( $TC_4 = 1$  line contains 4 instructions).

Therefore, this analysis of this experiment will not focus on a head-to-head comparison of the performance between the two caches. Instead we will focus on the performance of different trace cache configurations.

There are three sections analyzing the performance of the trace cache from different points of view. The first section shows the hit and miss counts on the trace cache while the capacity of the cache is increasing in both the width of the trace cache line and the number of trace cache lines. This section also shows hit and miss counts of the instruction cache to provide a reference point for trace cache performance.

The next section shows the percentage of hits and misses of the trace cache for different test programs. Hits and misses are presented in separated graphs to facilitate analysis of each of them individually. The last section displays how much of the trace cache space has been used and how much of it was left unused when the capacity of the trace cache is expanding. Please note that the words *trace cache* and *instruction cache* might be, from time to time, replaced with the abbreviations TC and IC, respectively.

#### 5.2 Hits and Misses of the Trace Cache

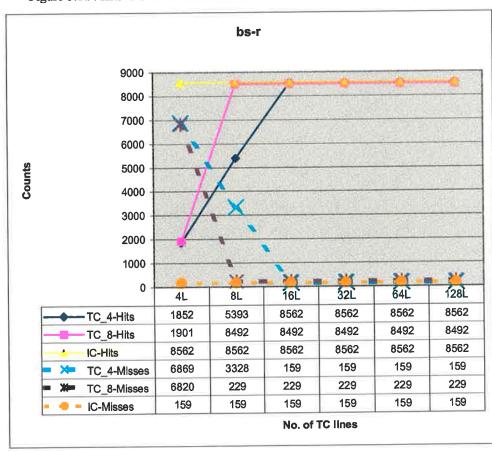

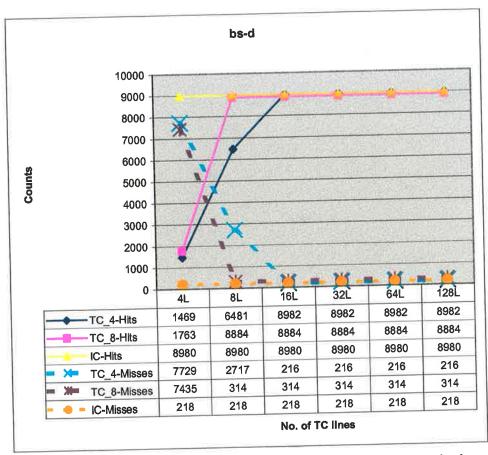

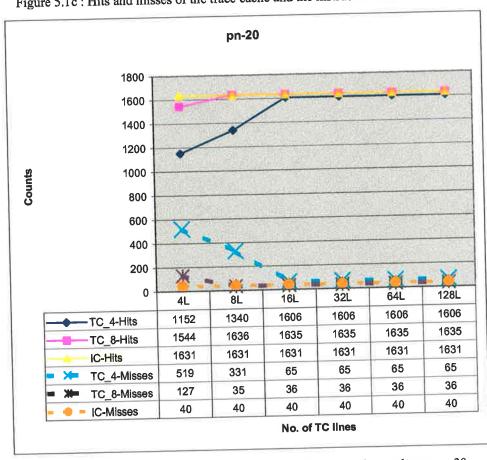

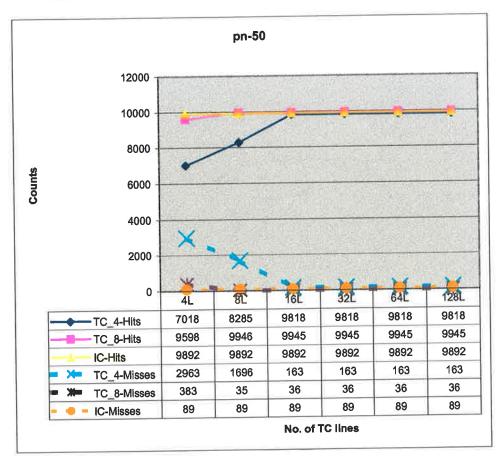

Fundamentally, the number of cache hits and misses is the performance indicator of cache memories. If there are more cache hits and fewer misses, it represents a better performance of the cache. This experiment has two main parameters that affect the performance of the trace cache when they vary, the size of a trace cache line and the total number of trace cache lines. The product of these parameters is actually the capacity of the trace cache but there may be different results for the same capacity from different parameter combinations because of the trace cache mechanism. Generally, a bigger trace cache capacity should perform better than a smaller one. However, it is essential to observe the actual results from these parameters that come into play with the fill policy in order to understand the design trade-offs.

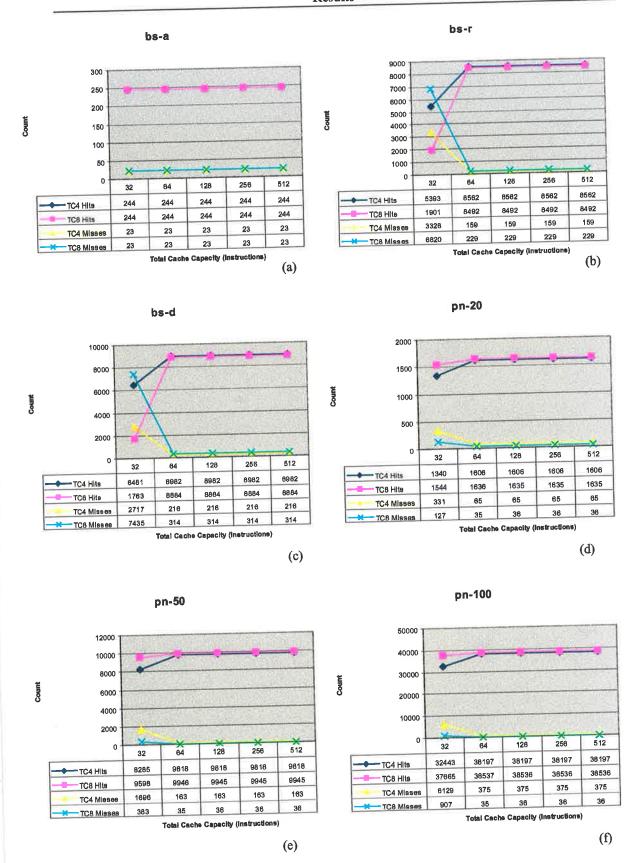

The results are presented as graphs with associated data tables of individual test programs (figures 5.1a to 5.1h). Each of them shows the acquired number of hits and misses of all configurations of the trace cache and also of the original instruction cache.

Figure 5.1a: Hits and misses of the trace cache and the instruction cache on bs-a.

Figure 5.1b: Hits and misses of the trace cache and the instruction cache on bs-r.

Figure 5.1c: Hits and misses of the trace cache and the instruction cache on bs-d.

Figure 5.1d: Hits and misses of the trace cache and the instruction cache on pn-20.

Figure 5.1e: Hits and misses of the trace cache and the instruction cache on pn-50.

Figure 5.1f: Hits and misses of the trace cache and the instruction cache on pn-100.

Figure 5.1g: Hits and misses of the trace cache and the instruction cache on Permute.

Figure 5.1h: Hits and misses of the trace cache and the instruction cache on DCT.

In general,  $TC_8$  performs better than  $TC_4$  in particular at the same number of TC lines except for DCT. Undoubtedly, the longer traces of  $TC_8$  increase the opportunity to find useful instructions in a single trace and the larger space allows more instructions to fit in and also decreases the chances of overwriting useful ones due to space contention. However, this advantage is not effective in every program as mentioned in the explanation above. The effectiveness depends on the pattern of dynamic execution of each particular program, so the advantage is not perfectly predictable.

For the case of bubblesort, TC\_8 at 4L is not as effective as TC\_4 because of two significant reasons evident from the raw data from the simulation (referencing the companion CD-ROM). This analysis is based on the comparison of 4L and 8L of bs-r and bs-d. The first reason is that 4L provides less space to hold useful traces long enough to offer required instructions and that particular traces were replaced by other traces that are not well used and live too long and, therefore, result in a lot of misses. The other reason is there is too much overwriting to the same line too frequently, so the useful traces cannot live long enough to produce hits. All of this is chiefly the problem of cache space contention combined with the direct-mapped scheme. Therefore, more TC lines can relax this drawback and offer more TC hit counts as we can see from the results.

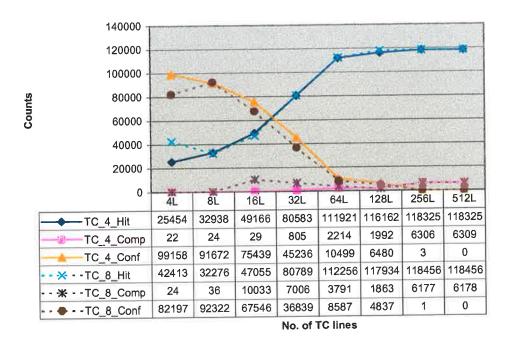

DCT is an exception from all of the graphs mentioned above. The performance of  $TC\_8$  is not better than  $TC\_4$  at the same number of TC lines. This peculiarity can be explained by the comparison graphs of TC hit, compulsory miss, and conflict miss of  $TC\_4$  and  $TC\_8$  in figure 5.2.

In the following discussion we refer to misses as either *compulsory misses* or *conflict misses*. When the line was selected at the first time but there is no instruction in it (valid bit = 0), it is called a *compulsory miss*. In contrast, if the selected line contains valid data but not the required instructions, it is called a *conflict miss*.

#### **DCT**

Figure 5.2: Comparison between TC hit and Compulsory Miss and Conflict Miss of DCT.