# Complexity Management and Modelling of VLSI Systems

Alex Dickinson B.E.(Hons)

A thesis submitted to the Faculty of Engineering for the Degree of Doctor of Philosophy.

Department of Electrical and Electronic Engineering

The University of Adelaide

South Australia

January 1988

# Contents

| $\mathbf{A}$ | bstra  | ct     |                                  | xi  |

|--------------|--------|--------|----------------------------------|-----|

| Pı           | reface | е      | x                                | iii |

| $\mathbf{A}$ | cknov  | wledge | ements                           | iv  |

| 1            | Intr   | oducti | ion                              | 1   |

|              | 1.1    | VLSI   | System Design Complexity         | 3   |

|              |        | 1.1.1  | Highly Partitioned Systems       | 5   |

|              |        | 1.1.2  | Functionally Partitioned Systems | 6   |

|              | 1.2    | Comp   | lexity and Structure             | 7   |

|              |        | 1.2.1  | Hierarchy                        | 9   |

|              |        | 1.2.2  | Regularity                       | 12  |

|              | 1.3    | Struct | cured Design                     | 13  |

|              |        | 1.3.1  | Abstraction                      | 14  |

|              |        | 1.3.2  | Modularity                       | 15  |

|              |        | 1.3.3  | Hierarchy                        | 16  |

|              |        | 1.3.4  | Information Hiding               | 17  |

|              |        | 1.3.5  | Limited Constructs               | 17  |

|              |        | 1.3.6  | Regularity                       | 18  |

|              |        | 1.3.7  | Design Procedures                | 20  |

|              | 1.4    |        | tural Design                     | 21  |

|              | 1.5    |        |                                  | 22  |

| 2 | Stru | ıctural | VLSI Design                         | <b>25</b> |  |  |  |  |  |  |

|---|------|---------|-------------------------------------|-----------|--|--|--|--|--|--|

|   | 2.1  | Softwa  | re Partitioning Criteria            |           |  |  |  |  |  |  |

|   |      | 2.1.1   | Coupling                            | 26        |  |  |  |  |  |  |

|   |      | 2.1.2   | Cohesion                            | 28        |  |  |  |  |  |  |

|   | 117  |         | 2.1.2.1 Summary                     | 31        |  |  |  |  |  |  |

|   | 2.2  | Struct  | ural Software Design                | 31        |  |  |  |  |  |  |

|   |      | 2.2.1   | Functional Decomposition            | 31        |  |  |  |  |  |  |

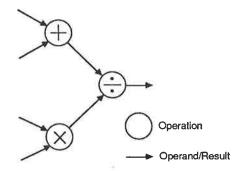

|   |      | 2.2.2   | Data Flow Design                    | 33        |  |  |  |  |  |  |

|   |      | 2.2.3   | Data Structure Design               | 34        |  |  |  |  |  |  |

|   |      | 2.2.4   | Summary                             | 35        |  |  |  |  |  |  |

|   | 2.3  | VLSI    | Partitioning Issues                 | 36        |  |  |  |  |  |  |

|   |      | 2.3.1   | Large Systems                       | 36        |  |  |  |  |  |  |

|   |      | 2.3.2   | Unstructured Mediums                | 37        |  |  |  |  |  |  |

|   |      | 2.3.3   | Concurrency                         | 37        |  |  |  |  |  |  |

|   |      | 2.3.4   | Communication                       | 38        |  |  |  |  |  |  |

|   |      | 2.3.5   | Packaging                           | 39        |  |  |  |  |  |  |

|   |      | 2.3.6   | Regularity                          | 40        |  |  |  |  |  |  |

|   |      |         | 2.3.6.1 Regularity of Function      | 40        |  |  |  |  |  |  |

|   |      |         | 2.3.6.2 Regularity of Interconnect  | 41        |  |  |  |  |  |  |

|   |      | 2.3.7   | Performance                         | 41        |  |  |  |  |  |  |

|   |      | 2.3.8   | Discussion                          | 41        |  |  |  |  |  |  |

|   | 2.4  | Abstr   | action and Hierarchical Equivalence | 42        |  |  |  |  |  |  |

|   | 2.5  | Struct  | tural VLSI Design                   | 44        |  |  |  |  |  |  |

|   |      | 2.5.1   | Planning and Construction           | 45        |  |  |  |  |  |  |

|   |      | 2.5.2   | Design Description                  | 47        |  |  |  |  |  |  |

|   |      | 2.5.3   | Modelling Algorithmic Function      | 47        |  |  |  |  |  |  |

|   |      | 2.5.4   | Modelling Physical Form             | 48        |  |  |  |  |  |  |

|   |      | 2.5.5   | Structural Design: Requirements     | 48        |  |  |  |  |  |  |

|   | 26   | Dalat   | ad Pasangah                         | 40        |  |  |  |  |  |  |

|   |     | 2.6.1  | Graph Partitioning             | 49        |

|---|-----|--------|--------------------------------|-----------|

|   |     | 2.6.2  | Stepwise Layout Refinement     | 49        |

|   |     | 2.6.3  | Partitioning Evaluation        | 50        |

|   |     | 2.6.4  | Integrated Descriptions        | 50        |

|   | 2.7 | Summ   | ary                            | 51        |

| 3 | A V | LSI D  | escription Language            | <b>52</b> |

|   | 3.1 | Introd | uction                         | 52        |

|   | 3.2 | Hardw  | vare Description Languages     | 53        |

|   |     | 3.2.1  | Register Transfer Descriptions | 53        |

|   |     | 3.2.2  | Token Passing Descriptions     | 54        |

|   |     | 3.2.3  | Provably Correct Descriptions  | 55        |

|   |     | 3.2.4  | Generalized Descriptions       | 56        |

|   | 3.3 | Langu  | age Requirements               | 57        |

|   |     | 3.3.1  | Function                       | 57        |

|   |     | 3.3.2  | Structure                      | 57        |

|   |     | 3.3.3  | Communication                  | 58        |

|   |     | 3.3.4  | Reusability                    | 58        |

|   |     | 3.3.5  | Regularity                     | 59        |

|   |     | 3.3.6  | Discussion                     | 59        |

|   | 3.4 | A Pro  | totype of the Language         | 60        |

|   | 3.5 | Select | ion of a Base Language         | 61        |

|   | 3.6 | Struct | tural Description              | 61        |

|   |     | 3.6.1  | Hierarchy                      | 62        |

|   |     | 3.6.2  | Interconnect ,                 | 63        |

|   |     | 3.6.3  | Structural Regularity          | 66        |

|   | 3.7 | Specif | ication of Function            | 67        |

|   |     | 3.7.1  | Declarations                   | 67        |

|   |     | 3.7.2  | Initialization                 | 67        |

|   |     | 0.70   |                                |           |

|   |      | 3.7.4                    | Specification of Time and Communication                                                                                                                                  | 68                               |

|---|------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |      | 3.7.5                    | Description of Time                                                                                                                                                      | 69                               |

|   |      | 3.7.6                    | Outgoing Communication                                                                                                                                                   | 69                               |

|   |      | 3.7.7                    | Incoming Communication                                                                                                                                                   | 70                               |

|   |      | 3.7.8                    | Synchronization                                                                                                                                                          | 70                               |

|   |      | 3.7.9                    | Bus Operations                                                                                                                                                           | 71                               |

|   | 3.8  | System                   | ns, Subsystems and Libraries                                                                                                                                             | 71                               |

|   | 3.9  | Param                    | neterization                                                                                                                                                             | 73                               |

|   | 3.10 | Limita                   | ations                                                                                                                                                                   | 74                               |

|   | 3.11 | An Ex                    | ample                                                                                                                                                                    | 75                               |

|   | 3.12 | Compa                    | arison                                                                                                                                                                   | 78                               |

|   |      | 3.12.1                   | Structural Description                                                                                                                                                   | 79                               |

|   |      | 3.12.2                   | Functional Description                                                                                                                                                   | 80                               |

|   |      | 3.12.3                   | Timing                                                                                                                                                                   | 80                               |

|   | 3.13 | Summ                     | nary                                                                                                                                                                     | 81                               |

| 4 | Mar  | J a 11! sa an            | Function: Simulation                                                                                                                                                     | 82                               |

| 4 |      | Ü                        |                                                                                                                                                                          |                                  |

|   | 4.1  |                          |                                                                                                                                                                          | 82                               |

|   | 4.2  | Functi                   | ional Modelling Requirements                                                                                                                                             | 83                               |

|   |      | 4.2.1                    |                                                                                                                                                                          |                                  |

|   |      | 0.0                      | Architectural Evaluation                                                                                                                                                 | 83                               |

|   |      | 2. 2                     |                                                                                                                                                                          | 83<br>84                         |

|   |      | · ,                      |                                                                                                                                                                          |                                  |

|   |      | 4.2.2                    | 4.2.1.1 Quantitative Evaluation                                                                                                                                          | 84                               |

|   |      | 4.2.2                    | 4.2.1.1 Quantitative Evaluation                                                                                                                                          | 84<br>86                         |

|   |      | 4.2.2                    | 4.2.1.1 Quantitative Evaluation         4.2.1.2 Qualitative Evaluation         Functional Verification                                                                   | 84<br>86<br>86                   |

|   |      | 4.2.2                    | 4.2.1.1 Quantitative Evaluation         4.2.1.2 Qualitative Evaluation         Functional Verification         4.2.2.1 Informal                                          | 84<br>86<br>86<br>88             |

|   | 4.3  | 4.2.3                    | 4.2.1.1 Quantitative Evaluation4.2.1.2 Qualitative EvaluationFunctional Verification4.2.2.1 Informal4.2.2.2 Formal                                                       | 84<br>86<br>86<br>88             |

|   | 4.3  | 4.2.3                    | 4.2.1.1 Quantitative Evaluation4.2.1.2 Qualitative EvaluationFunctional Verification4.2.2.1 Informal4.2.2.2 FormalSystem Integration                                     | 84<br>86<br>86<br>88<br>88       |

|   | 4.3  | 4.2.3<br>Design<br>4.3.1 | 4.2.1.1 Quantitative Evaluation 4.2.1.2 Qualitative Evaluation  Functional Verification 4.2.2.1 Informal 4.2.2.2 Formal  System Integration  and Implementation Overview | 84<br>86<br>86<br>88<br>88<br>88 |

|      | 4.5.1    | Conventional Representations          |

|------|----------|---------------------------------------|

|      | 4.5.2    | Definitions                           |

|      | 4.5.3    | Instances                             |

| 4.6  | Initiali | zation                                |

|      | 4.6.1    | Genesis                               |

|      | 4.6.2    | Instance Creation                     |

|      | 4.6.3    | Instance Hierarchy Creation           |

|      | 4.6.4    | Connection Creation                   |

|      | 4.6.5    | Port Declaration                      |

|      | 4.6.6    | Function Creation                     |

| 4.7  | Active   | Simulation                            |

| 4.8  | Comm     | unication and Scheduling              |

|      | 4.8.1    | Communication Semantics ,             |

|      | 4.8.2    | The Scheduling Problem                |

|      | 4.8.3    | Interprocess Communication Techniques |

|      | 4.8.4    | Demand Driven Scheduling              |

|      | 4.8.5    | Delay Driven Scheduling               |

|      | 4.8.6    | Discussion                            |

| 4.9  | Softwa   | re Organization                       |

| 4.10 | The Si   | mulator Interface                     |

|      | 4.10.1   | Translation and Compilation           |

|      | 4.10.2   | The Command Interpreter               |

|      | 4.10.3   | Browsing the Description Structure    |

|      | 4.10.4   | Error Detection and Notification      |

|      | 4.10.5   | System Stimulation                    |

|      |          | 4.10.5.1 Interactive                  |

|      |          | 4.10.5.2 File Based                   |

|      |          | 4.10.5.3 Language Based               |

|      | 4.10.6   | System Observation                    |

|   |      | 4.10.7  | Interactive                           |

|---|------|---------|---------------------------------------|

|   |      |         | 4.10.7.1 File Based                   |

|   |      |         | 4.10.7.2 Language Based               |

|   | 4.11 | Limita  | tions                                 |

|   | 4.12 | Summ    | ary                                   |

| 5 | Part | titioni | ng for Physical Form 120              |

|   | 5.1  | Introd  | uction                                |

|   | 5.2  | Constr  | raints in Physical Design             |

|   |      | 5.2.1   | Connection Length                     |

|   |      | 5.2.2   | Connection Area                       |

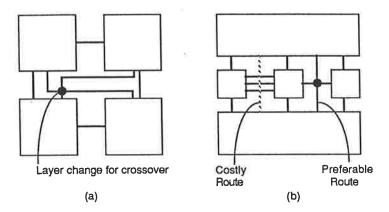

|   |      | 5.2.3   | Connection Planarity                  |

|   | 5.3  | Physic  | al Partitioning Techniques            |

|   |      | 5.3.1   | Highly Partitioned Designs            |

|   |      | 5.3.2   | Functionally Partitioned Designs      |

|   | 5.4  | Struct  | ured Floorplans                       |

|   | 5.5  | Creati  | ng Structured Floorplans              |

|   |      | 5.5.1   | Design Procedures                     |

|   |      |         | 5.5.1.1 Planning                      |

|   |      |         | 5.5.1.2 Sequencing                    |

|   |      | 5.5.2   | Designing with Rectangles             |

|   |      | 5.5.3   | Hierarchical Interactions             |

|   |      | 5.5.4   | Structuring Techniques                |

|   |      | 5.5.5   | Maintaining Planarity                 |

|   |      | 5.5.6   | Technology Independence               |

|   | 5.6  | Evalu   | ating Form with Structured Floorplans |

|   | 5.7  | Const   | ruction with Structured Floorplans    |

|   | 5.8  | Summ    | nary                                  |

| 6 | Mo   | delling | Form: Floorplanning 144               |

| 6.1 | Introd | uction     |                                      |

|-----|--------|------------|--------------------------------------|

| 6.2 | Appro  | aches to   | Automatic Floorplanning              |

|     |        | 6.21       | Planar Graph Techniques              |

|     |        | 6.22       | Slicing Techniques                   |

|     |        | 6.23       | Knowledge Based Techniques           |

|     | 6.2.1  | Discussion | on                                   |

| 6.3 | Knowl  | ledge Base | ed Design                            |

|     | 6.3.1  | Knowled    | lge Representation                   |

|     |        | 6.3.1.1    | Production Rules                     |

|     |        | 6.3.1.2    | Frames                               |

|     |        | 6.3.1.3    | Algorithms and Data Structures 159   |

|     | 6.3.2  | Reasonin   | ng Techniques                        |

|     |        | 6.3.2.1    | Abstraction                          |

|     | -      | 6.3.2.2    | Planning                             |

|     | ×      | 6.3.2.3    | Constraints and Least Commitment 162 |

|     |        | 6.3.2.4    | Backtracking                         |

|     |        | 6.3.2.5    | Metaknowledge                        |

|     |        | 6.3.2.6    | Inexact Reasoning                    |

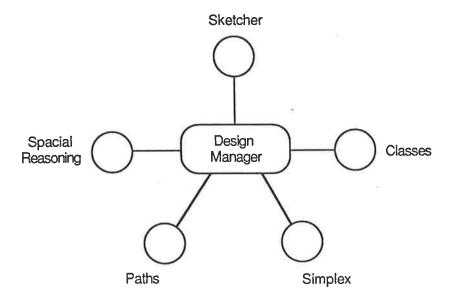

| 6.4 | System | n Overvie  | ew                                   |

| 6.5 | The S  | patial Re  | asoning Subsystem                    |

|     | 6.5.1  | The Rec    | ctangular Graph                      |

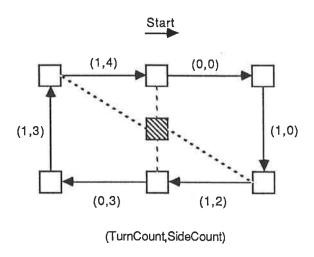

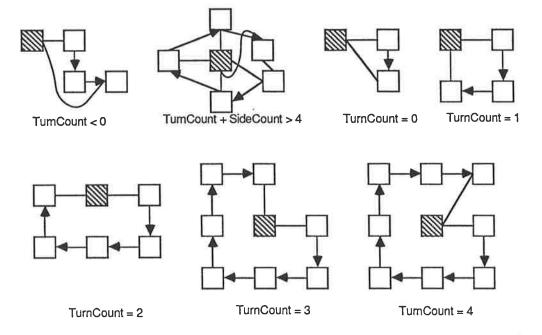

|     | 6.5.2  | Turning    | ;                                    |

|     | 6.5.3  | Propert    | ies of the Embedded RG               |

|     |        | 6.5.3.1    | Planar Embeddability                 |

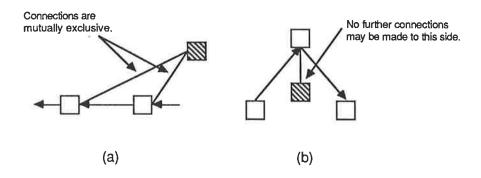

|     |        | 6.5.3.2    | Side Arcs                            |

|     |        | 6.5.3.3    | Triangulation                        |

|     | 6.5.4  | Ensurin    | g Feasible Placements                |

|     | 6.5.5  | Placeme    | ent Enumeration                      |

|     | 6.5.6  | The R.G    | Data Structure                       |

|      |         | 6.5.6.1 Pl    | acement     | Genera   | ation    | • 9   | •      | •              |        | •7 9 | (4)  | * 1            |      | •            |          | •    |        | 183 |

|------|---------|---------------|-------------|----------|----------|-------|--------|----------------|--------|------|------|----------------|------|--------------|----------|------|--------|-----|

|      |         | 6.5.6.2 Pl    | acement     | Accep    | tance    | e     | • •    | •              |        |      |      |                | · •  |              |          | * *  |        | 184 |

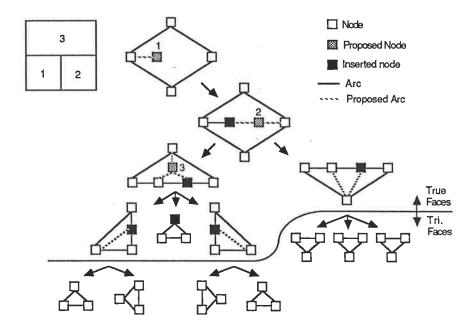

|      | 6.5.7   | Triangulation | on          |          |          |       |        | • 1            | • :•   |      | •    | • 0            |      | 900          | •        |      |        | 185 |

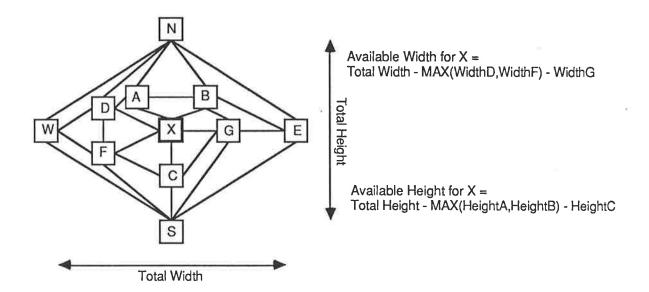

|      | 6.5.8   | Size Estima   | tion        |          |          |       |        | ,              |        | • 0  |      | • 19           | e .  | ( <b>.</b> ) |          |      | ٠      | 188 |

|      | 6.5.9   | Planarizatio  | on Suppo    | rt       |          | • 12  |        | (*)            |        | •0.0 | (*)  | • 0            | 60 ¥ | • • •        | e: (e    | * *  |        | 189 |

|      | 6.5.10  | Interface De  | efinition . |          |          | - 5   |        |                | • ••   | • •  | 3.00 |                |      |              | •2 :•    |      |        | 190 |

| 6.6  | The Cl  | asses Subsys  | stem        |          |          |       |        | ٠              | •      | ē 9  |      | • s            | s .  |              | n .      | • •  |        | 190 |

| 6.7  | The Pa  | aths Subsyst  | em          | • • •    |          |       |        | •              |        |      |      |                | 8    | •            |          |      |        | 193 |

| 6.8  | The Si  | mplex Subsy   | stem        |          | ٠        | •     |        | ٠              |        |      |      | ě 3            |      |              |          | • •  | •      | 195 |

| 6.9  | The Sl  | etcher Subs   | ystem       |          | e ser e  |       |        |                |        | ÷ /  |      | . (            | •    | •            |          | • •  | 9      | 196 |

| 6.10 | The D   | esign Manag   | ger         |          |          |       |        | i <b>s</b> 8 ( |        | •    |      | • 0            |      | •)           |          |      |        | 198 |

|      | 6.10.1  | Control Str   | ategies .   | e: 🖁 💌 🕬 | æ .s≆0 s |       | e 4    | •              |        | ¥. 5 |      | Sa II          | 8 8  | 546          |          |      | •      | 199 |

|      | 6.10.2  | Initializatio | n           |          | œ 0¥01 ¥ | - 340 |        | A RES          |        | * 0  | en 1 |                |      |              |          |      | •      | 201 |

|      | 6.10.3  | Planning      |             |          |          |       |        | () <b>•</b> () |        | * 1  |      |                |      | •            |          |      | 90     | 203 |

|      | 6.10.4  | Wait for Pl   | acements    |          |          |       |        | )•0 :          |        |      |      | •              |      | •            |          |      | 300    | 203 |

|      | 6.10.5  | Placement :   | Filtering   | * * *    |          |       |        | ·e: (          |        | •    | e •  | ii.            |      | 9€           |          |      |        | 204 |

|      | 6.10.6  | Module Sel    | ection      |          |          |       |        | •8:            |        | . :  | •: • |                |      | :•€          |          |      | 340    | 205 |

|      | 6.10.7  | Placement     | Selection   |          | e        | •     |        |                |        | * 1  | •    | ş•             | * *  | •            |          |      | 0.00   | 205 |

|      | 6.10.8  | Placement .   | Acceptan    | ce .     |          |       | • •    | •              |        | * 1  | • •  |                |      |              |          |      | (-0.00 | 208 |

|      | 6.10.9  | Constraint    | Propagat    | ion .    |          | ٠     |        |                |        | × ;  | • •  | 1.00           |      | •            |          |      | 7.0    | 208 |

|      | 6.10.10 | Deferred Ta   | asks        |          |          | •     |        |                |        |      | • •  | s <b>t</b>     |      |              |          |      |        | 209 |

|      | 6.10.11 | Planarizatio  | on Fault    | Handli   | ng ,     | •     |        | •              |        |      |      | ă <del>"</del> |      |              | • •      | •: • | ::::   | 209 |

|      | 6.10.12 | Route Com     | pletion     |          | [        | •     |        | •              |        | . 3  |      | ē              |      | •            | 5<br>• 1 | #: # | 3.0    | 210 |

|      | 6.10.13 | Solve         |             |          |          | •     |        | •              |        | . 3  |      | ē              |      | •            |          |      |        | 210 |

| 6.11 | Implem  | nentation .   |             |          |          | •     |        | V•(            |        | * 1  | 9    | (*)            |      |              |          |      | ٠      | 211 |

|      | 6.11.1  | Design Mar    | nager Imp   | olemen   | tatio    | n     |        | •              |        | •    |      | •              | 9.8  | ٠            |          |      | •      | 213 |

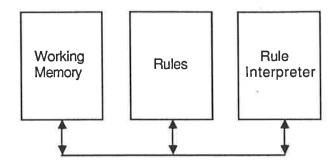

|      |         | 6.11.1.1 TI   | he Worki    | ng Me    | mory     |       |        |                |        | •    |      |                |      | ٠            |          |      | •      | 213 |

|      |         | 6.11.1.2 Tl   | he Rule S   | et       | × 100 s  |       |        | :•:            |        | ¥: : |      | 1. 1           |      | *            |          |      |        | 214 |

|      |         | 6.11.1.3 TI   | he Rule I   | nternr   | eter     |       | 20 100 | 1127           | w 0.50 |      |      |                |      |              |          |      |        | 216 |

|              |       | 6.11.2                                   | Subsyste    | m Implementat  | ions.    | ٠.                    | ٠.            |     |              |        |       |          |         | et te      | . 217 |   |

|--------------|-------|------------------------------------------|-------------|----------------|----------|-----------------------|---------------|-----|--------------|--------|-------|----------|---------|------------|-------|---|

|              |       |                                          | 6.11.2.1    | Symbols        |          |                       |               |     |              |        |       |          | ٠.      | • •        | 217   |   |

|              |       |                                          | 6.11.2.2    | Lists          |          |                       |               |     | •            |        | * *   |          | • •     | <b>€</b>   | . 219 | ł |

|              |       |                                          | 6.11.2.3    | Automatic Me   | mory l   | Man                   | age           | me  | nt .         |        |       |          |         |            | . 219 | i |

|              |       |                                          | 6.11.2.4    | Macros         |          |                       | • •           | • • |              |        |       |          | 8 8 8   | • •        | . 219 | 1 |

|              |       | 6.11.3                                   | Subsyste    | m Interface Me | chanis   | ms                    | • •           | • • |              |        |       |          |         |            | . 221 |   |

|              | 6.12  | Limita                                   | itions      | ******         |          |                       |               | a € |              | 21 2   | g 76  |          |         |            | 221   |   |

|              | 6.13  | Summ                                     | ary         |                |          |                       |               | • • |              | •      |       |          | 99      |            | . 222 | ) |

| _            | 4 0   |                                          | ın.         | G G 1          |          |                       |               |     |              |        |       |          |         |            | 00.4  |   |

| 7            |       |                                          | ,           | gn Case Stud   |          |                       |               |     |              |        |       |          |         |            | 224   |   |

|              | 7.1   |                                          |             |                |          |                       |               |     |              |        |       |          |         |            |       |   |

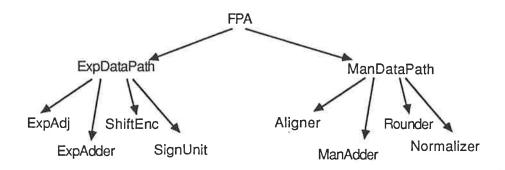

|              | 7.2   |                                          | Ü           | ple            |          |                       |               |     |              |        |       |          |         |            |       |   |

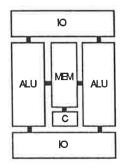

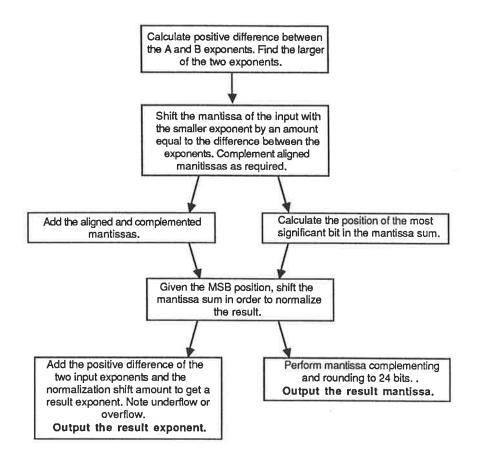

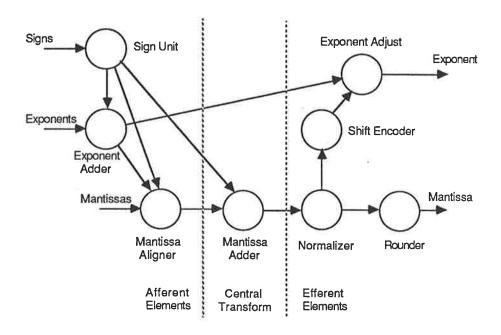

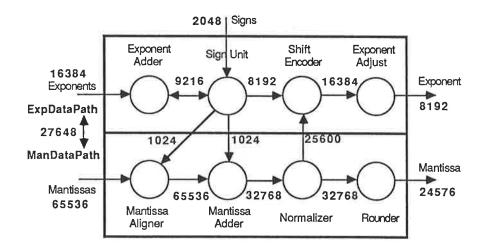

|              | 7.3   | Functi                                   | onal Ove    | rview          |          | * 9*9                 | ¥ %           | * 8 |              | 36 ¥   | ian v |          | : • ·   | 4 4        | . 226 | ) |

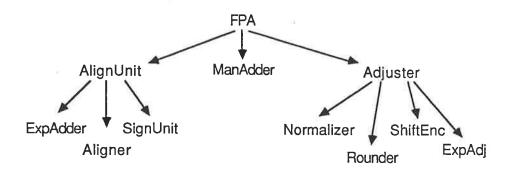

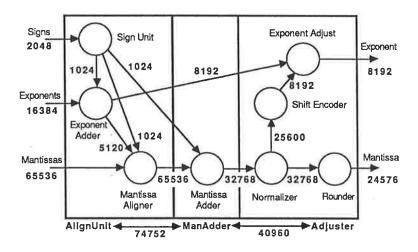

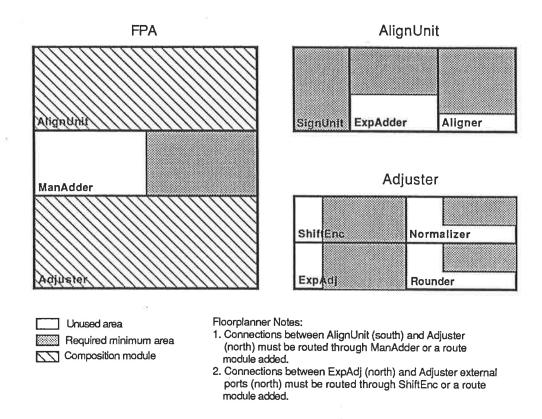

|              | 7.4   | An Ini                                   | itial Parti | tioning        |          | •                     |               |     | <i>i</i> = 2 | •      |       | w ni     |         |            | . 226 | ; |

|              |       | 7.4.1                                    | Specifica   | tion           |          |                       | <b>1</b> . 14 |     |              |        | •     | · · ·    |         | * *        | . 228 | 3 |

|              |       |                                          | 7.4.1.1     | The Alignmen   | t Unit   | <b>*</b> 5 <b>*</b> 0 |               |     | W 5          |        |       | 24 H     | : × :=  | : ¥: 34    | . 229 | ) |

|              |       |                                          | 7.4.1.2     | The Mantissa   | Adder    | • 3•3                 |               |     |              |        | 500 B |          | - × ×   | ) ¥6 9¥    | . 230 | ) |

|              |       |                                          | 7.4.1.3     | The Adjuster   |          | • 00                  |               | * * |              |        | 300   |          | e (* 5* | E 10 (10 H | . 230 | ) |

|              |       |                                          | 7.4.1.4     | The FPA Con    | npositio | on                    |               |     | •: :         |        |       |          | e o• o• | * *        | . 232 | 2 |

|              |       | 7.4.2                                    | Modellin    | g Function     |          | • (%)                 |               |     |              |        |       | · ·      |         |            | . 233 | } |

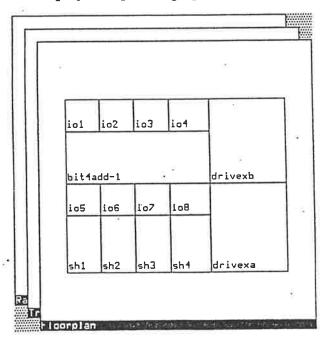

|              |       | 7.4.3                                    | Modellin    | ig Form        |          | ÷ ÷                   |               |     |              |        |       |          |         |            | . 234 | 1 |

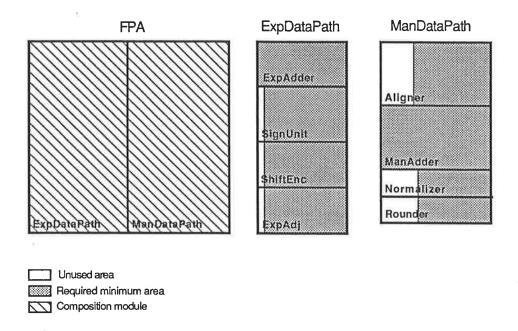

|              | 7.5   | 7.5 Discussion and Modified Partitioning |             |                |          |                       |               |     | . 23         | ó      |       |          |         |            |       |   |

|              | 7.6   | Refining the Exponent Adder              |             |                |          |                       |               |     |              | . 238  | 3     |          |         |            |       |   |

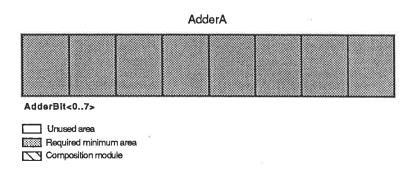

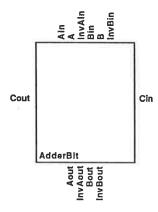

|              | 7.7   | Refini                                   | ng the A    | lder           |          |                       |               |     |              |        |       |          |         |            | . 24  | 1 |

|              | 7.8   | Summ                                     | ary         |                | * * * *  | BH 24                 |               |     |              | 8 28 8 | 25 3  | 1 1983 3 |         | : iii iii  | . 24  | 5 |

|              |       |                                          |             |                |          |                       |               |     |              |        |       |          |         |            |       | _ |

| 8            | Cor   | ıclusio                                  | n           |                |          |                       |               |     |              |        |       |          |         |            | 246   | j |

| $\mathbf{R}$ | efere | nces                                     |             |                |          |                       |               |     |              |        |       |          |         |            | 249   | 9 |

#### Abstract

The major objective of the research described in this thesis is to describe effective methods for the partitioning of Very Large Scale Integrated (VLSI) systems.

A comparison is made between the structural design of large programs and large VLSI designs. A methodology for VLSI structural design is proposed based on many of the precepts of structural program design. The methodology requires restructuring of the design process; a specific form of design representation; and the addition of computer aided modelling of both the algorithmic function and geometrical form of the structural design.

The design process is divided into a designer intensive top-down planning phase, and an automatic bottom-up construction phase.

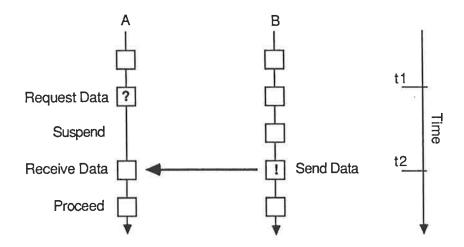

A model of design is described in which the commonly used layered set of abstractions are replaced by a single structural description. The language introduced for this purpose incorporates a number of features to reduce the apparent complexity of the system description. The abstract representation of intermodule synchronization and communication allows a process of stepwise refinement to be applied to these as well as the more usual structural entities.

Two computer aided modelling tools have been developed that together constitute a facility for rapidly analyzing alternate structural partitionings in the search for an acceptable design.

The first computer aided modelling tool is a functional simulator incorporating a novel interprocess communication and scheduling mechanism. This allows the efficient implementation of the description language intermodule communication semantics. The interactive nature of the simulator facilitates initial debugging and qualitative evaluation of the design. A profiling facility allows for the quantitative evaluation of the partitioning based on data flow and module activity.

The second computer aided modelling tool is a hierarchical floorplanner that facilitates the evaluation of the embedding of the proposed structural design into the plane. An investigation of structured floorplan design shows that the process is inherently knowledge intensive, and that much of that knowledge is inexact. The floorplanner incorporates several novel knowledge representations that are used to express diverse classes of designer expertise. A representation for spatial reasoning provides for the

efficient manipulation of rectangles in a mosaic. Another representation has been developed for reasoning with the inexact knowledge used by designers in predicting the implementation of floorplan modules in a hierarchical design. A production system is used as a design manager to guide the overall development of the design.

A case study is presented that demonstrates the utility of the methodology and computer aided design tools in VLSI system design.

# Preface

This thesis contains no material which has been accepted for the award of any other degree or diploma in any University. To the best of the author's knowledge and belief the thesis contains no material previously published or written by another person, except where due reference is made in the text.

The author hereby consents to this thesis being made available for photocopying and loan if accepted for the award of the degree.

Alex Dickinson

# Acknowledgements

Many people have contributed (sometimes unwittingly) to the effort represented by this thesis. Some of them are named here.

My Australian supervisor, Kamran Eshraghian, set me on this path, and provided the enthusiasm, confidence, and encouragement required to get me to the end. Neil Weste, my US supervisor, was instrumental in getting me there and provided much good advice. Special thanks to Neil and Avril (together with Miles and Ellen) for their support when I arrived zombie-like in New Jersey, and to John and Jenny for their friendship and lovely sweaters. Thanks also to Peter Cole, who acted as my supervisor in Kamran's absence, for being both appreciative and fun to work with over (though sometimes quite infuriating!).

Thanks to Integrated Silicon Design and The Association for Computing Machinery for providing the travel support that enabled me to flit about and greatly increase my knowledge (and time in the sun). The Commonwealth Department of Education provided the regular source of funds needed to make a PhD possible, and Tim Gent was stalwart in dealing with my odd requests. Bell Labs, and in particular the people of lab 1135 generously provided me with facilities and a whole new area of knowledge. Martin Levy patiently taught me the basics of Unix hacking and introduced me to the joys of the Redbank diner at 3am. Many thanks especially to Bryan Ackland, who seems to have endless patience with me, and whos calm, quiet advice I greatly value. Thanks to Alan Huang for his confidence in my abilities and for offering me a challenging opportunity.

Thanks to Charles Watson for reviewing the thesis, and Greg Zyner for his help with the case study. Thanks to the people at Bell Labs, Symbolics, and other institutions who gave up their time to drink coffee and discuss floorplan design.

Other far-away people that I would like to thank include Graham Birtwistle in Calgary and Wolfgang Fichtner in Zurich for their useful comments and travel assistance. Honestly, I didn't just visit to get up into the mountains...

To the residents of the postgraduate tea room and members of the Flat Earth Society go my thanks for providing hundreds (thousands?) of hours of entertaining conversation. On some days the only motivation I found to come into work was to sit and talk. I'd like to thank Mike Pope for his dry humor, his spelling ability, and

for joining with me in meandering hacker's conversations.

Mike Liebelt provided generous access to computer facilities (no matter how extreme and frivolous the demands I made on them!), together with teaching me how to confound a bureaucracy. More important though was his quiet confidence that I was going somewhere, his patience with me, and marvelously calm and sensible advice on dealing with many problems, both technical and personal. Thanks Mike.

To my parents and brother go my boundless thanks for their patience and support in dealing with an eternal student, both emotionally and financially, especially in my time away. Dad, I wish you could be here to see it finished, you were always so proud.

There's only one more. Thanks Pru for your faith, generosity, patience, understanding, caring, and love. This thesis is for you my friend.

# Chapter 1

# Introduction

The major objective of the research described in this thesis is to describe effective methods for the partitioning of Very Large Scale Integrated (VLSI) systems.

The philosophy of structured programming is regarded as one of the most effective methodological tools used to manage software complexity [Dijkstra, 1972]. The application of structured programming techniques to VLSI systems was proposed by Carver Mead at Caltech [Mead & Conway, 1980] and has since been widely adopted for the design of custom integrated circuits.

A central principle of this structured VLSI design methodology is the partitioning of systems into a hierarchy of modules. However techniques for generating such a structure are not well developed. In this thesis the inherent difficulties of partitioning VLSI systems are examined and methods proposed for solving the problem. These structural VLSI design methods are intended to complement those of the established structured VLSI design methodology.

The concepts involved in the structural design of programs [Yourdon & Constantine, 1975] are used in this thesis as an aid to the development of a methodology for structural VLSI design. It will be argued that the horizontally layered abstraction used for design representation in structured VLSI design are well suited to the structural planning task. An alternative method based on the parallel development of algorithmic function and physical form will be described.

Central to the methodology are a design specification language and two interlinked design aids for *modelling* the structural design. The architectural specification language provides for the abstract representation of the structure and function of the

proposed design. The first modelling aid is a simulator for the language that is used to evaluate the functional partitioning of the design. The second modelling aid is a knowledge-based floorplanner that assists in the evaluation of the partitioning on the two dimensional silicon surface. The use of knowledge-based techniques allows the floorplanner to operate in a top-down design style and incorporate principles of structured VLSI layout design. These two design aids constitute a facility for rapidly analyzing alternate structural designs in the search for an acceptable result.

In the remainder of this chapter the problem of VLSI design complexity is described together with the established structuring techniques used in its control. The deficiencies of such techniques are discussed and the relevance of *structural design* is introduced.

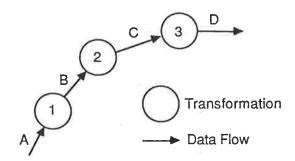

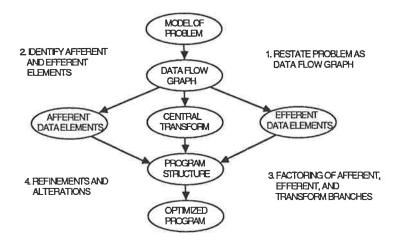

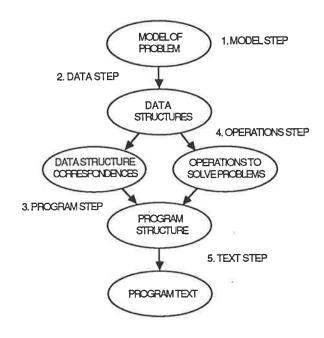

In Chapter 2 a description is given of the methods developed for the creation and evaluation of structural designs for programs. The difficulties of partitioning VLSI systems are examined, and the similarities and differences between the two domains identified. A structural VLSI design methodology is then described based on a reorganization of the VLSI design process. This allows software structural design techniques to be used in VLSI given the existence of appropriate languages and design aids.

A language designed for the abstract description of VLSI designs is described in Chapter 3. The language has a number of features that assist in the abstract description and refinement of structure and communication in the design.

The functional modelling of VLSI designs is discussed in Chapter 4. A simulator is described that models the behaviour of a design to aid in the evaluation of the functional partitioning.

The issues involved in producing a system partitioning suitable for physical design—floorplanning—are examined in Chapter 5.

In Chapter 6 a knowledge-based floorplanner is described that allows for the modelling of the structural design in terms of its realization as a floorplan.

An example of design using the previously described methodology and design aids is documented in Chapter 7.

Finally conclusions and suggestions for further research that arise from this thesis are given in Chapter 8.

# 1.1 VLSI System Design Complexity

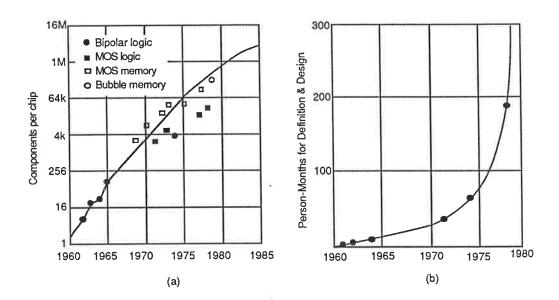

In 1964 Gordon Moore predicted that integrated circuit complexity (as measured by device count) would continue to double every year: the ubiquitous "Moore's Law" [Noyce, 1977]. Since 1970 however this line has only been held to by memory devices. Less regular designs have fallen below the predicted complexity as shown in Figure 1.1(a) [Moore, 1979]. This lag exemplifies the problem that now faces VLSI design: the complexity of the design task has risen to the point where it is difficult for designers to create systems that make full use of the available fabrication processes. This has resulted in an exponential rise in design effort as illustrated in Figure 1.1(b).

Figure 1.1: Trends in integrated circuit complexity [Moore, 1979].

The complexity of VLSI design may be attributed to two related phenomena: the lack of *structure* in, and difficulty of *communication* on, the silicon surface.

The structuring problem results from the essentially unstructured nature of the VLSI medium—there is no a priori partitioning imposed on the design. According to Séquin [Séquin, 1983] this may result in a dangerous situation where the complexity within a large, unstructured domain simply overwhelms the designer.

Large digital systems are typically exhibit a great deal of physical partitioning. Transistors are integrated into IC's, IC's are placed onto PC boards, PC boards are connected to mother boards, mother boards are packaged into cabinets and interconnected with backplane buses.

The partitioning of systems into such a packaging (or physical) hierarchy is guided by factors such as division of labor, clarity of design, ease of manufacture, functionality, communication requirements, reliability, testability and maintainability. This structure is an artifact imposed by design influenced by physical considerations, not an innate property of the medium — one could (however inadvisably) attempt to design and build a complex digital system on a single circuit board in a completely unstructured manner.

There is no innate structuring imposed by the physical nature the VLSI medium. The entire planar silicon surface is available, and any structure is imposed by the designer.

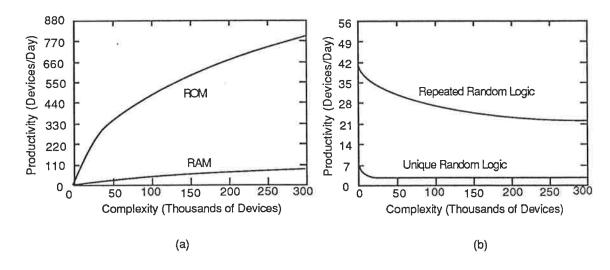

Some VLSI design problems are inherently well structured. Memory design, for instance, has achieved high circuit densities limited mainly by fabrication technology rather than design complexity [Taylor & Johnson, 1985]. This may be attributed to the their simple regular structure and consequent design in which a small number of circuit blocks are designed and replicated for placement in a regular pattern of interconnection. For designs with less inherent structure such as those based round instruction sets and protocols, the additional design complexity has a profound effect on designer productivity. This is illustrated in Figures 1.2(a) and 1.2(b). In memory design an economy of scale is achieved: as the number of devices increases, design productivity increases. In the design of less well structured elements, not only is productivity about an order of magnitude less, it actually decreases with circuit complexity.

Figure 1.2: Designer productivity [Fey, 1985].

The general approach to improving designer productivity in such cases is to utilize the freedom that exists in the VLSI domain to impose different structuring schemes on the silicon surface in order to reduce design complexity. Prior to introducing two broad classes of structuring VLSI designs it is useful to briefly examine the issue that differentiates them: the design of the *interconnect* used for communication within the structure.

There are three primary costs associated with integrated circuit interconnect:

- 1. Area. Longer wires consume more design area. This results in less functionality being implemented in a given area.

- 2. Speed. Longer wires result in greater RC time delays for a fixed sized driver.

- 3. Power. Greater capacitive loads on drivers result in higher power consumptions.

Interconnect length and complexity has in fact been identified as one of the primary fundamental limits on circuit integration [Keyes, 1981]. Keyes also notes that it is one of the few such limits for which there is no underlying physical theory, further complicating design near that limit.

The need to reduce interconnect length must be traded off against the need to simplify design to increase productivity. This trade-off may be observed between the two major classes of VLSI structuring: *highly* partitioned and *functionally* partitioned systems [Ferry, 1985]. They are described in the following two sections.

# 1.1.1 Highly Partitioned Systems

It is possible to impose a structure similar to that use in conventional digital design onto unstructured silicon. Gate array and standard cell "semi-custom" design styles cluster the atomic components of the design, the transistors, into small functional units. These are then placed and routed such that area and interconnect length are minimized. The procedure is quite analogous to the production of printed circuit board designs, and a large number of algorithms have been created or adapted for the automation of this design task, a recent example being simulated annealing [Sechen & Sangiovanni-Vincentelli, 1985]. These design styles are termed highly partitioned in that they are structured into a large number of small partitions.

The primary disadvantages of such design styles stems from the expense incurred by communication between the components on the two-dimensional surface. Keyes refers to a typical gate-array design of 1496 gates in which  $0.26cm^2$  of the total chip area of  $0.32cm^2$  is used for the running of 4m of interconnect [Keyes, 1981]. This implies an active are of only 20%, the remaining 80% being utilized for long wire runs with their attendant disadvantages.

In summary, highly partitioned styles have the advantage of being amenable to design by automated techniques because of the simple formulation of design as place and route. However the large area consumed by wiring precludes them from achieving transistor packing densities sufficient for VLSI levels of integration (> 10<sup>5</sup> transistors per die).

#### 1.1.2 Functionally Partitioned Systems

In order to achieve VLSI levels of integration it is necessary to resort to design styles based around functional partitioning. In these styles the system is decomposed into modules that are functionally related, resulting in a reduction in the amount of communication that occurs between partitions. The increased circuit densities achievable with this form of partitioning may be attributed to an associated reduction in interconnect. Ferry's results suggest that average interconnect lengths in a VLSI circuit that is functionally partitioned do not continue to increase as device sizes are scaled down and chips become more densely packed [Ferry, 1985]. He cites the functionally partitioned design of the HP 32b microprocessor. It contains  $1.3 \times 10^5$  gates with 5m of interconnect, implying a factor of 70 reduction in the wiring length per gate ratio over the gate array design referred to previously. Ferry relates the success of functional partitioning to a reduction in information flow between design partitions, a concept discussed further in Chapter 2.

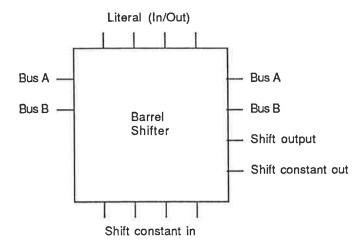

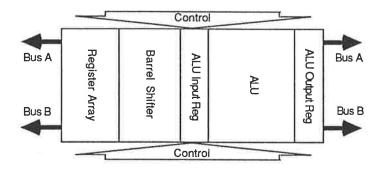

Functionally partitioned designs are generally produced using a full custom design style. Not only is the design functionally partitioned, but the design of the resulting layout takes into account the geometrical interactions of the connecting modules. This minimizes inter-partition communication costs. In this way modules may be designed so as to combine their function with the needs of system communication, a classic example being the barrel shifter (Figure 1.3). The interconnect required by the shifter matches the global interconnect strategy of the data-path illustrated in

Figure 1.9.

Figure 1.3: A structured layout design for a barrel shifter [Mead & Conway, 1980, p. 161].

The use of functional partitioning and custom design techniques adds considerably to the complexity of the design task compared to highly partitioned design styles. Not only must module interfaces be carefully designed to decrease interconnect costs, but the higher resulting device densities increase the number of components in the design.

Fey's research [Fey, 1985] supports the contention that the primary complexity problem of VLSI design is that of interconnect: the productivity model he describes predicts that a custom circuit of 10<sup>6</sup> devices will take about 400 man years of effort to design in 1989, however an increase in the complexity of interconnect could increase this by an order of magnitude.

In the following section an examination is made of some general complexity management techniques. The application of these techniques to functional partitioning in structured VLSI design is discussed in Section 1.3.

# 1.2 Complexity and Structure

In order to provide a basis for the discussion of structured design as a complexity management technique, the relationship between design complexity system structure shall be examined in this section. The complexity of a system comprised of a number of parts may be defined as the way in which a whole is different from the composition of the parts [Van Emden, 1975]. In other words, complexity is that property of a system that arises from the fact that it is a composition of a number of parts: before the parts were composed they may be regarded as having zero complexity as a reference point. This definition emphasizes that aspect of complexity of particular interest in system design: that the complexity of a system is due to the interaction of its parts.

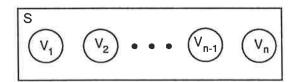

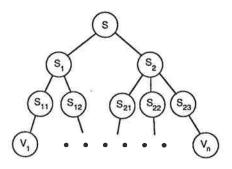

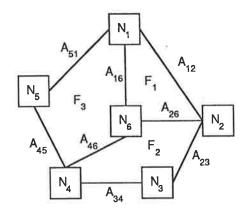

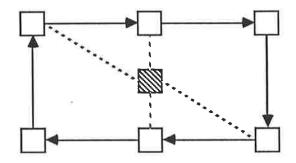

We can express the complexity of a system in terms of the interactions between its parts as follows. For the system S composed of atomic components  $V_{1..n}$  illustrated in Figure 1.4 the complexity C(S) may be expressed in terms of R, the interaction between atomic components as:

$$C(S) = R(V_1, V_2) + R(V_1, V_3) + \dots + R(V_1, V_n)$$

+  $R(V_2, V_3) + \dots + R(V_2, V_n) + \dots$

$\dots + C(V_1) + \dots + C(V_n)$

Figure 1.4: An unstructured system S composed of atomic components  $V_1 \cdots V_n$ .

In accordance with Van Emden's definition only the difference between the total complexity and the sum of the complexities of the atomic components is of interest:

$$C(S) - C(V_1) - \dots - C(V_n) =$$

$$R(V_1, V_2) + R(V_1, V_3) + \dots + R(V_1, V_n)$$

$$+ R(V_2, V_3) + \dots + R(V_2, V_n) + \dots$$

The sum of the atomic component complexities may then be treated as a zero level of complexity finally giving the complexity of the system as a sum of the interactions of the parts:

$$C(S) = R(V_1, V_2) + R(V_1, V_3) + \dots + R(V_1, V_n) + R(V_2, V_3) + \dots + R(V_2, V_n) + \dots$$

$$(1.1)$$

The *structure* of a system is the manner in which the component parts are organized to form a whole. We shall present a system as having two classes of structure: *implicit* and *explicit*.

Implicit structure. The implicit structure of a system is a property of its basic construction, not its description. The implicit structure tends to be intricate as it covers a systems function, physical partitioning and any other features of its operation and appearance. Systems have a corresponding implicit complexity [Séquin, 1983] that is a function of their construction: the number of components and their interactions.

Explicit structure. The explicit structure of a system is a property of a particular representation used to describe it to an observer. The explicit complexity [Séquin, 1983] implied by such a structure is a function of the representation, and as such is amenable to reduction by judicious choice of representation.

For example, a VLSI chip has an intricate implicit structure of perhaps hundreds of thousands of transistors each carrying out complex manipulations of charge carriers across junctions, and communicating via current carrying wires and capacitive coupling. When describing such a device, structuring and abstraction techniques may be used to generate a description that implies a much simpler explicit structure, and a correspondingly reduced explicit complexity.

A general approach to the problem of reducing explicit system complexity is to produce a simple explicit structure by describing the system in a *structured* manner: simplifying part (component) interactions by means of *hierarchy* and *regularity*.

## 1.2.1 Hierarchy

One of the simplest forms of structuring that may be applied to a system is that of partitioning. Recursive application of partitioning gives rise to a hierarchical system: a system that is composed of interrelated subsystems, each of the latter being, in turn hierarchical in structure until we reach some lowest level of elementary subsystem [Simon, 1962].

The components of a subsystem typically have non-uniform intensities of interaction. This non-uniformity is a useful basis for defining a hierarchical partitioning of the system. Strongly interacting components may be clustered into subsystems, and the resulting subsystems interact in relatively less complex manner. If a system is amenable to such a recursive partitioning it is known as nearly decomposable as opposed to a decomposable system in which the subsystems are effectively independent [Simon, 1962].

The judicious application of hierarchical structuring techniques to a system can reduce the explicit complexity of that system in a number of ways which may be qualitatively described as follows:

- 1. The task of dealing with the system is simplified because only the components and interactions of a single subsystem need be considered at a time.

- 2. Sufficient application of hierarchical partitioning results in simple elementary components  $(V_{1..n})$ .

- 3. In each subsystem, each child subsystem may be represented by an *interface* that hides information other than that relevant to the composition of the child subsystems.

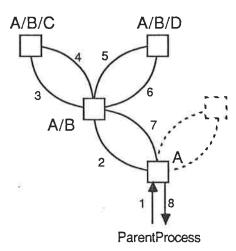

Van Emden [Van Emden, 1975] presents the following analysis of the effect of using hierarchical structures. If the whole is different from the parts then this difference is due to the interaction of the parts. The magnitude of this interaction is equal to the difference between the complexity of the whole and the sum of the complexities of the parts. For the system S composed of subsystems  $S_{ij}$  and atomic components  $V_{1..n}$  illustrated in Figure 1.5 the complexity C(S) may be expressed in terms of R, the interaction between subsystems as:

$$C(S) = R(S_1, S_2) + C(S_1) + C(S_2)$$

$$= R(S_1, S_2) + R(S_{11}, S_{12}) + R(S_{21}, S_{22}, S_{23})$$

$$+ C(S_{11}) + C(S_{12}) + C(S_{21}) + C(S_{22}) + C(S_{23})$$

This decomposition can be continued to give C(S) as a function only of subsystem interactions and  $C(V_1) \cdots C(V_n)$ , the complexities of the atomic components:

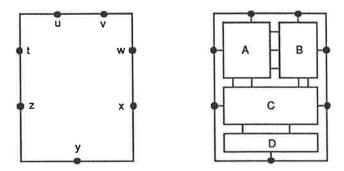

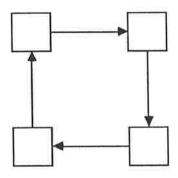

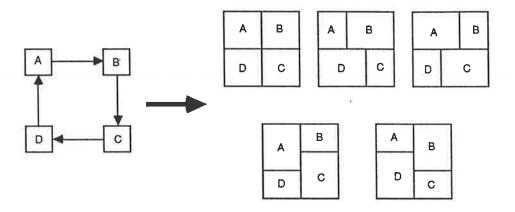

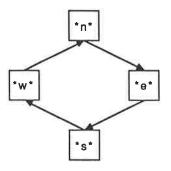

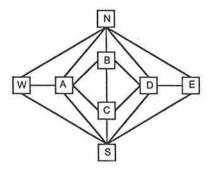

Figure 1.5: A simple hierarchically structured system.

$$C(S) = R(S_1, S_2) + R(S_{11}, S_{12}) + R(S_{21}, S_{22}, S_{23}) + \cdots$$

$$\cdots + C(V_1) + \cdots + C(V_n)$$

Under Van Emden's definition only the difference between the total complexity and the sum of the complexities of the atomic components is of interest:

$$C(S) - C(V_1) - \dots - C(V_n) = \dots$$

$R(S_1, S_2) + R(S_{11}, S_{12}) + R(S_{21}, S_{22}, S_{23}) + \dots$

The sum of the atomic component complexities may then be treated as a zero level of complexity finally giving the complexity of the system as a sum of the interactions of the parts:

$$C(S) = R(S_1, S_2) + R(S_{11}, S_{12}) + R(S_{21}, S_{22}, S_{23}) + \cdots$$

(1.2)

The advantages of the hierarchical structuring compared to the non-hierarchical case (Equation 1.1) are:

- 1. There are typically fewer R (interaction) terms to be considered: only one for each subsystem. This contrasts to the non-hierarchical case in which there was an R term for each pairwise combination of atomic components.

- 2. The R (interaction) terms are independent: each subsystem  $S_{ij}$  appears only in one term. This simplifies the design of subsystems that minimize interaction with other subsystems.

Quantification of the interaction of the parts (R) is domain dependent, and will be discussed further in Chapter 2. The effectiveness of a partitioning at reducing complexity within a particular level of the hierarchy may however be expressed in terms of two basic concepts: coupling and cohesion [Yourdon & Constantine, 1975]. Coupling is a measure of the interaction between subsystems: lower coupling implies less interaction and hence less complexity. Cohesion is a measure of how well the components of a subsystem belong together. Coupling and cohesion may be used as criteria for designing system partitions, and will be discussed in detail in Chapter 2.

The vocabulary for the description of hierarchical systems varies with the domain under study and often even within a domain. In this thesis, general subsystems will be referred to as modules, subsystems composed of further subsystems will be referred to as composition modules, subsystems that are components of a composition shall be referred to as submodules, and elemental subsystems will be referred to as leaf modules. The terms module and cell are synonymous, although module will be preferred.

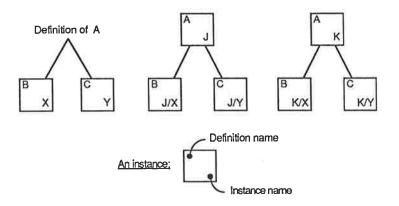

#### 1.2.2 Regularity

The explicit representation of regularity in a system description is a powerful structuring technique. For example two systems A and B may be composed of a similar number of components with similar amounts of interaction and hence have similar implicit complexity. However if the structure of A can be expressed in terms of the simple replication of some module and its interconnections, then the explicit complexity of A relative to B is greatly reduced. Here we suggest that this reduction in complexity has two sources:

1. Regularity of function. Systems such as A contain a degree of redundancy in their implicit structure that may be made use of by judicious partitioning into identical modules. These may then be expressed as the multiple instances of a single module definition. Explicit complexity is reduced as only the definition must be considered in depth, each instance simply being a replication of the definition. This form of complexity reduction may be quantified by a simple regularity factor: the total number of components divided by the number that must be individually constructed. This is also illustrative of the difference between explicit and implicit complexity. The actual number of components

(implicit complexity) is unchanged, but their description (explicit complexity) has been simplified.

2. Regularity of interaction. In a system such as A that is amenable to division into identical modules, the interaction patterns between the identical instances will also tend to be regular. Such regular patterns of interaction reduce complexity simply by reducing R, the degree of interaction between subsystems.

The need to distinguish between these two classes or regularity arises because one may occur without the other. In particular, regular interaction patterns may be used to add structure to a system that has little functional redundancy in its implicit structure. Examples of functional and communication regularity in a VLSI system are given in Section 1.3.6.

# 1.3 Structured Design

The structured design style is a loose collection of techniques and principles that aid in the development systems in a structured manner in order to control design complexity.

The early formalization of structured design evolved in the domain of complex software systems. The increasing size of software projects in the 1960's gave rise to a situation in which few systems met goals, schedules or budgets [Brooks, 1975]. Researchers perceived that the problem was in part at least due to a lack of structure in the design domain, and this drove the development of a number of software structuring techniques that have become known collectively as structured programming [Dijkstra, 1972]. These techniques are quite diverse and based on number of principles including: abstraction, modularity, hierarchy, information hiding, regularity, and step-wise refinement.

The principles of structured programming have been widely adopted and are regarded as instrumental in controlling the complexity of the software problem [Brooks, 1975, p. 144].

The application of structured design to VLSI followed from the realization that in common with software design, VLSI design had reached a crisis point in complexity and this was to a considerable degree due to a lack of structure in the design process (Section 1.1). The formulation of structuring techniques for VLSI design is typified by the *Caltech Structured Design Methodology* promulgated by Mead and Conway [Mead & Conway, 1980]. Many of these techniques have been adapted from structured programming to the two dimensional domain of VLSI design.

The remainder of this section provides an overview of the principles of structured VLSI design derived from a number of sources including [Mead & Conway, 1980; Buchanan, 1980; Rowson, 1980; Trimberger et al., 1981; Mudge et al., 1980b; Tucker & Scheffer, 1982; Lattin et al., 1981]. Where appropriate, parallels between structured VLSI design and structured programming will be drawn.

#### 1.3.1 Abstraction

Structured system are particularly amenable to the application of abstraction as a means of simplifying their descriptions. Abstraction involves the development of a vocabulary that is well matched to the problem domain, suppressed irrelevant detail, that is translatable into the target vocabulary of the design.

In programming, high level languages (HLL) can be used to provide just such an abstraction. Each HLL construct is an abstraction of the underlying instruction set that performs some function appropriate to the problem domain. Examples include if...then for the expression of alternation and for...do for the expression of iteration.

The task of translating an HLL to machine code, though not trivial, requires only a small "conceptual distance" to be bridged as there is a simple relationship between many of the concepts in both the HLL and machine language: for example many architectures provide an subroutine call instruction, well matched to HLL procedure call constructs.

In VLSI, the conceptual distance between the system specifications and the target vocabulary (a mask description language) is far greater: the two have very few concepts in common. The response to this has been the development of a series of levels of abstraction. The levels suggested in the Caltech design methodology are:

- 1. Behavioural. Description of the system function without necessarily specifying any structure. For instance ISPS [Barbacci, 1981] represents behaviour in terms of an instruction set specification.

- 2. Structural. Description of the system as a set of interconnected components,

each contributing to the overall behaviour.

3. Physical. Description of the system as a set of interconnected physical components, each having a direct implementation as a mask entity.

In each case the uppermost level is intended to provide a vocabulary suited to expressing the system behaviour, and successive levels are designed to provide representations incrementally closer to the target mask level. The sequence of levels divides the large conceptual distance into smaller steps that can each be bridged by the human designers assisted by computer, or in some cases by translation or compilation programs alone.

Silicon compilers attempt to bridge the conceptual distance between system specification and mask in a single step, and typically this can only be done by narrowing the problem domain of a such compiler to a single target architecture: this allows the creation of a set of simple abstractions that can be used during the translation of specification to layout. Silicon compilers that generate high quality layout across a spectrum of architectures do not appear likely in the near future [Werner, 1982].

#### 1.3.2 Modularity

The advantages of decomposing a system into a number of interacting components or modules was described in Section 1.2.1. In VLSI design the basic gains are in both ease of design and reduction in computation. The functional description can be partitioned into modules, reducing the complexity of individual design tasks, and allowing the application of multiple-person design teams working on independent problems. The actual amount of design work that needs to be performed may be reduced by the development of libraries of commonly used modules. The partitioning of a VLSI system is more complex than that of a software system because of the added physical constraints of shape, size and geometrical signal interface that exist in VLSI at the physical layout level.

. Modularity achieves computational gains in the area of design verification: only modules that have been altered need be re-verified by for instance simulation and design rule checks, traditionally expensive procedures.

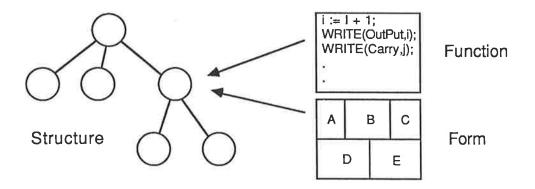

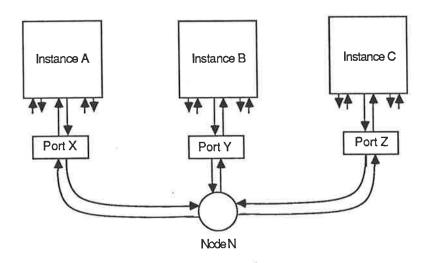

The motivations for the use of modularity in software are very similar. The main difference is the implementation of the principle in the two domains and the complexity of the partitioning task. Re-use of modules in software (for instance math libraries) is more common as interfaces are simpler, having only logical and not physical manifestations. Typically an analogy is drawn between modules in VLSI and procedure calls in software, however a more appropriate analogy is that of coroutine or process structures [Hoare, 1978] in which the entities have a continuous existence and carry out computation in parallel. This hardware/software relationship can be used to advantage as will be shown in Chapter 4.

#### 1.3.3 Hierarchy

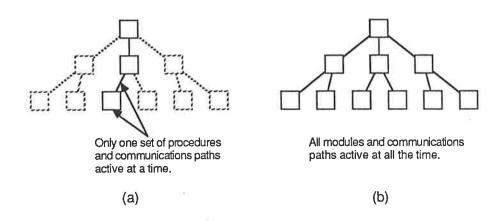

The use of hierarchy makes it possible to decompose the design in order to control the number of submodules that occur in a particular composition module, allowing control of composition module complexity. In irregular design sections, the hierarchy may be made deeper with a lower branching factor to keep the module count in the realm of Miller's estimate of human information processing capacity of seven items [Miller, 1956]. In regular sections of design, the branching factor can be increased to make use of repetition of identical modules and communication patterns (Section 1.3.6).

A particular aspect of the use of hierarchy in structured VLSI design is the restriction to a separated hierarchy [Rowson, 1980]. In such a hierarchy a distinction is made between those cells that comprise the leaf nodes of the hierarchy and all other non-leaf nodes. Actual active circuitry may only be present in the leaf nodes, all other nodes consisting of simple interconnections of leaf or non-leaf nodes. This separation of hierarchy allows the definition of mathematical operators for operations on the hierarchy, treating it purely as a recipe for the combination of functional units (the leaves). Such operators have been defined for analysis [Rowson, 1980] and structural assembly [Watson, 1985] of separated hierarchies.

An unresolved issue in structured VLSI design is whether there should be identical hierarchies used in the description of the system at different levels of abstraction, or whether for the sake of simplicity, there should only be a single hierarchical structure. This issue is addressed further in Chapter 2.

In the software domain, hierarchical decomposition is used in design in a similar manner to reduce complexity. Typically the elements of the hierarchy are subroutines rather than processes.

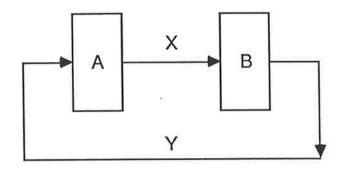

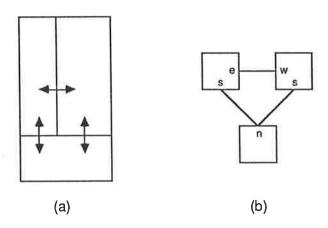

#### 1.3.4 Information Hiding

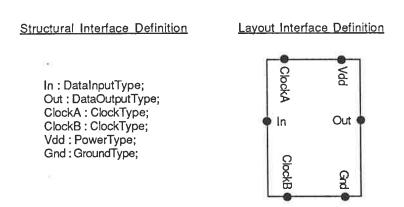

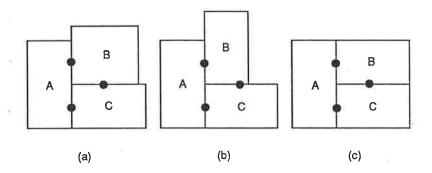

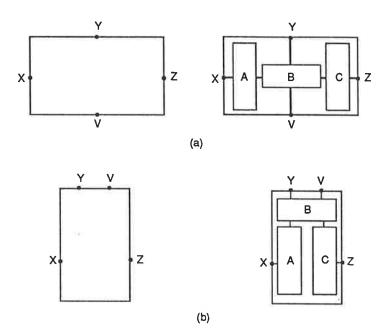

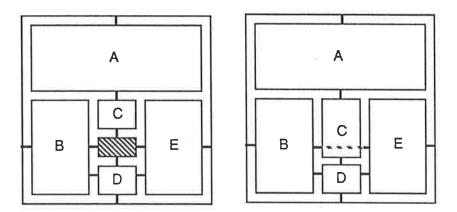

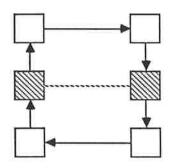

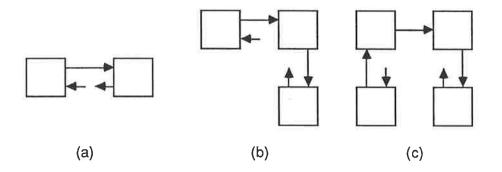

Closely tied to the principles of modularity and hierarchy is that of information hiding: in the construction of a composition module from a number of submodules, the submodules are represented by an interface that presents only that information relevant to composition task. The nature of these interfaces varies over the range of design abstractions. At the structural level an interface may consist only of the names and types of logical signal pathways into the module, while at the physical level the interface must include information about port positions, layers, and module size and shape amongst other things. Figure 1.6 illustrates some of the interface criteria at different levels of abstraction. At all times the interface should only specify the minimum necessary information to keep the intellectual complexity of the design task as low as possible. Information hiding by means of module interfaces plays a major part in top-down design: submodules may be used as components in a composition prior to their implementation.

Figure 1.6: Information hiding by module interface design.

Information hiding in VLSI and software engineering are analogous: in software the details of a subroutine's implementation may be specifically separated from its interface.

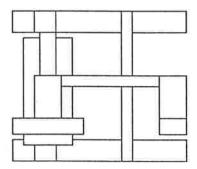

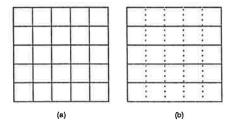

#### 1.3.5 Limited Constructs

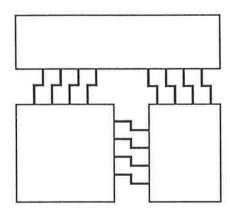

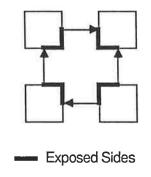

One method for reducing the ease with which designers may create invalid layout structures is to limit the nature and number of the components that may be used in the design, and limit the means for composing them into larger structures. In structured VLSI design this principle is applied in several areas. Firstly, designers are only permitted the use of "Manhatten" geometries in which all edges meet at right angles (Figure 1.7). This makes designs clearer in intent, reduces the margin for error by reducing for instance the number of configurations of transistors, and simplifies the construction and computational cost of design and verification tools. Secondly, layout modules may only have rectangular boundaries which must not overlap during composition and module interconnection may only occur over adjacent edges of modules via pre-defined ports: this simplifies the tasks of module composition and verification.

Figure 1.7: A layout using only "Manhatten" geometries.

The structured programming principle of limiting program structures to those of concatenation, limited selection and iteration based round the theoretic work of Böhm and Jacopini [Böhm & Jacopini, 1966] is analogous to the limited structures of structured VLSI design. In addition the syntax rules of a HLL preclude the generation of certain errors resulting from incorrect use of the limited constructs available. The limitation that layout modules communicate only through predefined ports is closely related to the software concept of parameter passing in function calls: data should only be transferred through explicitly declared channels, not via global accesses. Alternately, since in software modules communicate by means of control transfers in addition to data transfers, it is possible to equate communication through module ports with the avoidance of goto based global control transfers [Dijkstra, 1968].

# 1.3.6 Regularity

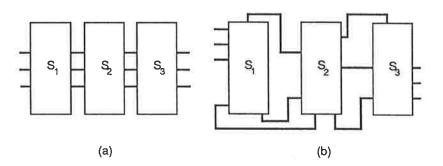

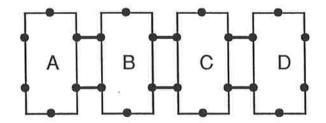

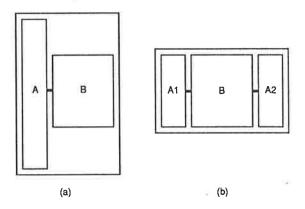

As discussed in Section 1.2.2, there are two aspects to regularity in structured systems: function and interaction. Regularity in function is achieved by the imposition of an appropriate partitioning on the design. Replicating modules has a number of

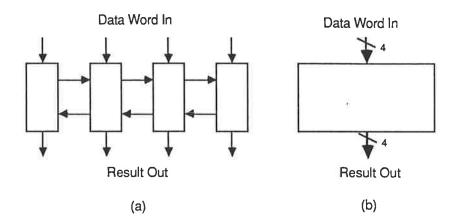

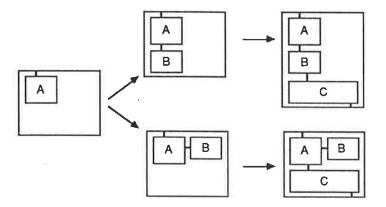

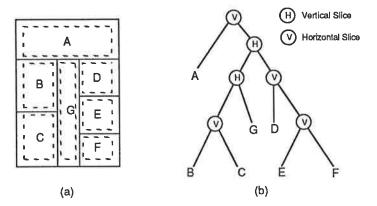

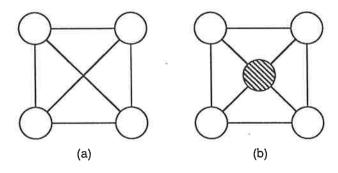

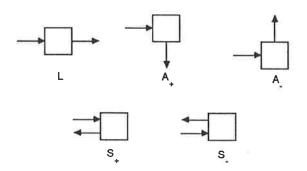

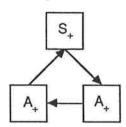

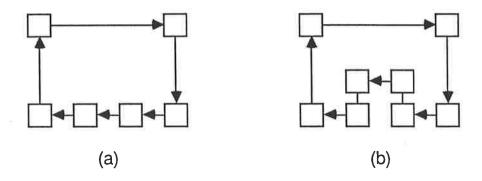

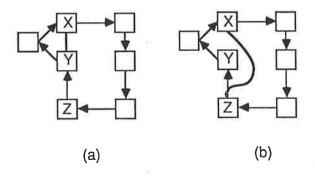

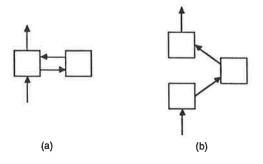

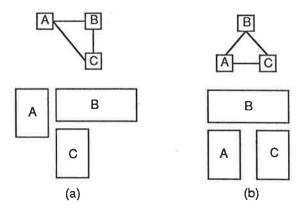

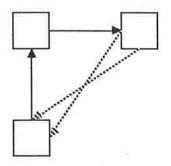

advantages. The complexity of the representation is reduced, leading to greater perpescuity. Design and computational savings are made in that only a single module need be designed/verified and then simply instanced a number of times. Figure 1.8 illustrates how functional regularity appears at the layout level, and how it may or may not be accompanied by regular communication patterns.

Figure 1.8: Functional regularity in a register set with (a) and without (b) regular interconnect.

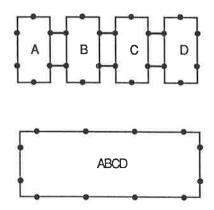

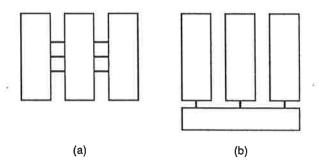

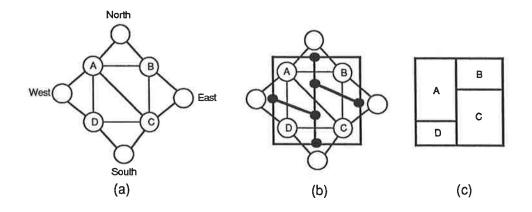

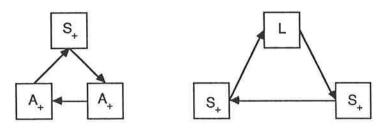

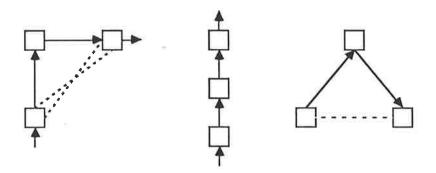

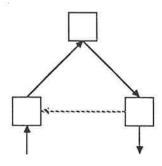

Functional regularity tends to be a property of the low levels of large system hierarchies: within such elements as registers, adders and multipliers. At higher levels large systems (other than memories) are in general composed of non-identical modules. It is at this level that regularity in communication may be used to lower the complexity of module interactions. Figure 1.9 illustrates a data path in which the component modules have been designed with the aim of being interconnected according to a regular pattern.

Figure 1.9: A data path segment: elements are connected in a regular fashion [Mead & Conway, 1980, p. 166].

The most appropriate software analogy to functional regularity is the application of

a function to a regular data structure. For example an image may be represented as a two dimensional array, and then the iterative application of a simple function to that array may be used to process the image—a single piece of code is used a number of times over a regular structure.

The use of interconnect regularity in software is less apparent, as the relative simplicity of intermodule communication makes it less necessary.

#### 1.3.7 Design Procedures

Both structured VLSI design and structured programming are amenable to top-down design procedures in which the initial specifications are decomposed into smaller subproblems, a process that is applied recursively until the subproblems are small enough to be simply implemented by a block of layout or code. This process has been characterized in software as one of "stepwise refinement" [Wirth, 1971]. At each step in the decomposition, a set subroutines is proposed that when connected via their interfaces will perform the desired composite function. In this way the interfaces are designed first and guide the later implementation of the subroutines. Top-down design in structured VLSI is an analogous process in which modules are refined into interconnected submodules [Van Ginneken & Otten, 1984]. There are two primary differences in the application of stepwise refinement in the two domains:

- 1. The decomposition in the VLSI domain forms a *plan* that is used for the eventual bottom-up assembly of the layout blocks into a final design. In software there is no analogous assembly process, the "plan" simply being the procedure call sequence.