## Fault Tolerance in VLSI

Paul D. Franzon B. Sc., B. E. (Hons.)

A thesis submitted to the

Department of Electrical and Electronic Engineering, the

University of Adelaide, to meet the requirements for award of the degree of

Doctor of Philosphy.

December 1988.

#### Abstract

A primary goal in microelectronic systems progress is the achievement of yet higher levels of functional integration. Today this is being addressed from two different perspectives: Firstly, introducing more circuitry onto the chips themselves and; secondly, packaging the chips in higher performance media.

Wafer-Scale Integration (WSI), whereby the chip assumes the size of a wafer, is one goal that combines elements from both of these perspectives. A purely advanced packaging approach is Hybrid Wafer-Scale Integration (HWSI), or silicon on silicon thin film hybrids. Both of these approaches offer many potential advantages, in terms of speed, reliability, power consumption, packaging density and cost. The potential advantages, as well as the disadvantages, are discussed in detail before a review of current WSI and HWSI projects is presented.

Currently one factor that limits chip size growth are the defects incurred in the production of any integrated circuit. Defect tolerance provides the means to overcome this limitation and is particularly important for the achievement of WSI.

A critical point in evaluating approaches to defect tolerance for VLSI, WSI and Ultra Large Scale Integration (ULSI) is the yield model used. A correct yield model allows the type and amount of the optimal level of defect tolerance to be determined. A yield model is presented here that takes account of both clustering and the influence of the reconfigurable interconnect. Two different approaches are presented which would be used for different modeling applications: yield, and expected number of connected processors. The latter form has a number of advantages. The model is applied to a VLSI signal processing chip, and to a generalized chip, to determine the kind of chip structures that can best benefit from defect tolerance. It is found that in order to benefit from defect tolerance regular structures covering more than 20% to 30% of the chip are required. The yield model is also applied in a consideration of granularity effects on wafer-scale arrays. As a result of this discussion on granularity a new metric is suggested for evaluating array element architectures.

Using this model as a basis, a number of alternative approaches to WSI are presented and evaluated. After a review of existing approaches, during which a suitable classification system is introduced, a new approach, called the "frame" approach is introduced. The frame scheme is aimed at the WSI implementation of 2D arrays, containing reasonably large elements. The design and implementation of WSI and HWSI examples of the "frame" scheme are presented. Practical lessons learnt about implementing WSI and HWSI designs are also discussed.

Finally a detailed comparison of different approaches to implementing 2D arrays in WSI is undertaken. The relative merits of the frame scheme are affirmed in this section. Examples are presented that demonstrate the relative advantages and disadvantages of the various approaches, indicating the important points to be considered when designing wafer scale arrays.

# Contents

| 1 | Intr | oduction 1                                 |

|---|------|--------------------------------------------|

|   | 1.1  | Research Outline                           |

|   | 1.2  | Advanced Packaging Technologies            |

|   | 1.3  | Potential Benefits of WSI                  |

|   |      | 1.3.1 Size and Weight                      |

|   |      | 1.3.2 Reliability                          |

|   |      | 1.3.3 Reduced Power Requirements           |

|   |      | 1.3.4 Performance                          |

|   |      | 1.3.5 Production Costs                     |

|   | 1.4  | Difficulties to be Overcome to achieve WSI |

|   | 1.5  | Hybrid WSI                                 |

|   | 1.6  | Three Dimensional Packaging                |

| 2 | Wo   | rld Status of WSI                          |

|   | 2.1  | History of WSI                             |

|   | 2.2  | Major WSI Projects                         |

|   |      | 2.2.1 ESPRIT 824 Program                   |

|   | 2.3  | Major Hybrid WSI Projects                  |

|   | 2.4  | Three Dimensional Packaging                |

| 3 | Yie  | ld Modeling 34                             |

|   | 3.1  | Faults in Silicon                          |

|   | 3.2  | Non Fault Tolerant Yield Models            |

|   | 3.3  | Fault Tolerant Yield Modeling              |

|   | 3.4  | Fault Tolerant Chip Memories               |

|   | 3.5  | Yield Modeling for Processor Arrays        |

|   |      | 3.5.1 Yield Formulation                    |

|   |      | 3.5.2 Expected Number of PEs               |

|   |                | 3.5.3   | Effects of Clustering                                                                                                                             | 52         |

|---|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |                | 3.5.4   | Comparison with other fault tolerant yield formula                                                                                                | 53         |

|   | 3.6            | Critica | l Area Determination                                                                                                                              | 54         |

|   |                | 3.6.1   | Purpose of Critical Area Determination                                                                                                            | 54         |

|   |                | 3.6.2   | General Methodologies and Related Work                                                                                                            | 54         |

|   |                | 3.6.3   | Critical Area Determination for the Transform and Filter Brick                                                                                    | 57         |

|   | 3.7            | Detern  | nination of Optimal Redundancy for TFB                                                                                                            | 57         |

|   |                | 3.7.1   | Fault Tolerant Control Store                                                                                                                      | 60         |

|   | 3.8            | Granul  | larity and Defect Tolerant Chips                                                                                                                  | 61         |

|   | 3.9            | Granul  | larity in Wafer Scale Arrays                                                                                                                      | 63         |

|   | 3.10           | Modeli  | ng Interconnect Yield in Reconfigurable Circuits                                                                                                  | 72         |

|   | 3.11           | Place o | of Yield Simulation in Defect Tolerant Design                                                                                                     | 80         |

| 4 | $\mathbf{Red}$ | undan   | cy Techniques for Wafer Scale Arrays                                                                                                              | 82         |

|   | 4.1            | Redun   | dancy through Reconfiguration                                                                                                                     | 82         |

|   | 4.2            | Reconf  | figuration Technologies                                                                                                                           | 84         |

|   | 4.3            | Archite | ectures for WSI                                                                                                                                   | 92         |

|   | 4.4            | Tradeo  | offs in Redundancy Schemes                                                                                                                        | 93         |

|   | 4.5            | Linear  | Arrays                                                                                                                                            | 94         |

|   | 4.6            | Mesh A  | Arrays                                                                                                                                            | 98         |

|   | 4.7            | Tree S  | tructures                                                                                                                                         | 98         |

|   | 4.8            | Maxim   | izing the Speed of a Wafer-Scale Array                                                                                                            | 03         |

|   | 4.9            | Conclu  | sions                                                                                                                                             | 04         |

| 5 | 'Chi           | p Fran  | ne' Scheme for Reconfigurable Mesh-Connected Arrays 1                                                                                             | 06         |

|   | 5.1            | Introdu | $\operatorname{action} \ldots \ldots \ldots \ldots \ldots \ldots 1$                                                                               | 06         |

|   | 5.2            | Reconf  | iguration Scheme                                                                                                                                  | 08         |

|   |                | 5.2.1   | Approaches to Fault Tolerance $\dots \dots \dots$ | 08         |

|   |                |         | 5.2.1.1 Detailed Scheme Description                                                                                                               | 15         |

|   | 5.3            | Global  | Reconfiguration in Response to Faults                                                                                                             | 18         |

|   |                | 5.3.1   | Global Reconfiguration in Response to Faults for 1D Arrays $1$                                                                                    | 24         |

|   |                | 5.3.2   | Global Reconfiguration in Response to Faults - Mesh Arrays . 1                                                                                    | 25         |

|   |                |         | 5.3.2.1 Scheme Utilization                                                                                                                        | <b>2</b> 5 |

|   | 5.4            | Throug  | shput Rate Optimization                                                                                                                           | 26         |

|   |                | 5.4.1   | RC Model                                                                                                                                          | 29         |

|   |                | 5.4 2   | WSI Driver Proposals                                                                                                                              | 31         |

|   |      |         | 5.4.2.1                                        | ADVICE Results                              | ٠.  | 133         |  |  |  |  |

|---|------|---------|------------------------------------------------|---------------------------------------------|-----|-------------|--|--|--|--|

|   |      | 5.4.3   | Discussi                                       | on of Modeling Results                      |     | 133         |  |  |  |  |

|   |      |         | 5.4.3.1                                        | Choice of Approach and Area-Time Optimality |     | 134         |  |  |  |  |

|   |      |         | 5.4.3.2                                        | Power Dissipation                           |     | 135         |  |  |  |  |

|   |      | 5.4.4   | Conclus                                        | ions                                        |     | 137         |  |  |  |  |

|   | 5.5  | Fault   | Detection                                      | and Isolation                               | • • | 137         |  |  |  |  |

|   | 5.6  | Imple   | nentation                                      | 1                                           |     | <b>13</b> 8 |  |  |  |  |

|   | 5.7  | Summ    | ary                                            |                                             |     | 139         |  |  |  |  |

| 6 | Cor  | nparin  | g Redur                                        | ndancy Approaches for Mesh Arrays           |     | 152         |  |  |  |  |

|   | 6.1  | Comp    | arison Me                                      | etrics                                      |     | 152         |  |  |  |  |

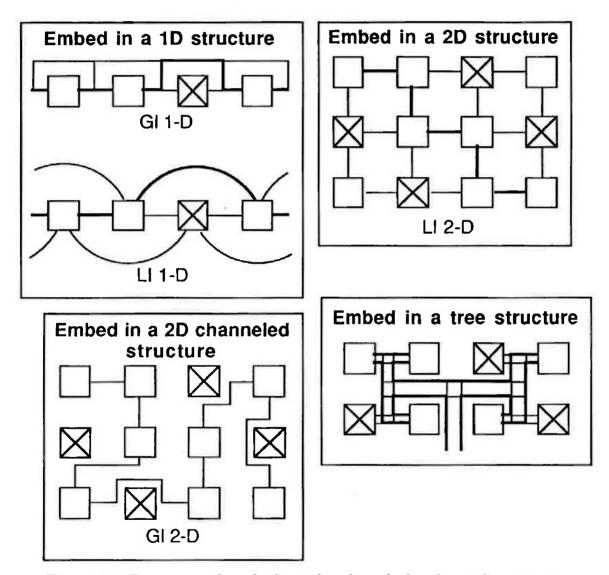

|   | 6.2  | Classi  | fication of                                    | f Mesh Arrays                               |     | 154         |  |  |  |  |

|   | 6.3  | Comp    | arison of                                      | Mesh Redundancy Approaches                  |     | 166         |  |  |  |  |

|   |      | 6.3.1   | Monte C                                        | Carlo Simulation                            |     | 166         |  |  |  |  |

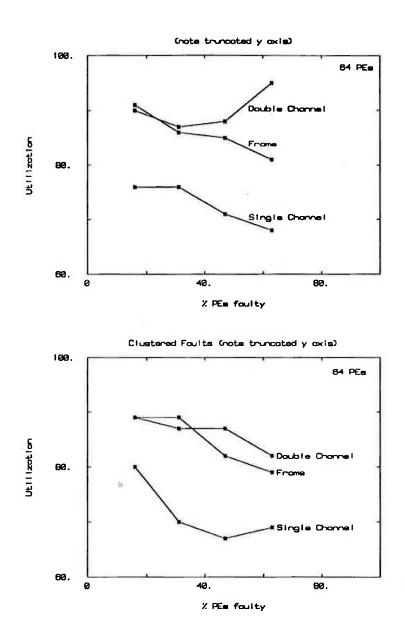

|   |      | 6.3.2   | Utilizati                                      | on Comparisons                              |     | 170         |  |  |  |  |

|   |      |         | 6.3.2.1                                        | Effect of array size                        |     | 178         |  |  |  |  |

|   |      |         | 6.3.2.2                                        | Effect of Clustering                        |     | 180         |  |  |  |  |

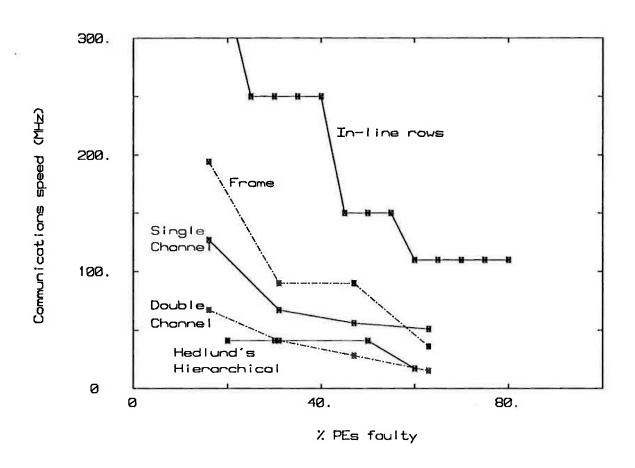

|   |      | 6.3.3   | Speed C                                        | Comparisons                                 |     | 187         |  |  |  |  |

|   | 6.4  | Overa   | Overall Comparison of Different Scheme Samples |                                             |     |             |  |  |  |  |

|   | 6.5  | Impro   | ved Scher                                      | nes                                         |     | 211         |  |  |  |  |

| 7 | Cor  | clusio  | ns                                             |                                             |     | 214         |  |  |  |  |

|   | 7.1  | Defect  | Tolerand                                       | e and Advanced Packaging                    | • • | 214         |  |  |  |  |

|   | 7.2  | Yield : | Modeling                                       | for Fault Tolerant VLSI and WSI             |     | 215         |  |  |  |  |

|   | 7.3  | Makin   | g WSI an                                       | nd HWSI Parts Using the Frame Scheme        |     | 216         |  |  |  |  |

|   | 7.4  | Compa   | arison Stu                                     | idies of Fault Tolerant Mesh Arrays         |     | 217         |  |  |  |  |

|   | 7.5  | Future  | Work .                                         |                                             | ٠.  | 220         |  |  |  |  |

| • | D 1  | 3.6     |                                                |                                             |     |             |  |  |  |  |

| A | Dela | ау Мо   | aels                                           |                                             |     | 221         |  |  |  |  |

| В | Pub  | lished  | Papers                                         |                                             |     | 224         |  |  |  |  |

# List of Figures

| 1.1 | Substrate efficiency                                                                                      | 5          |

|-----|-----------------------------------------------------------------------------------------------------------|------------|

| 1.2 | Cost-density relationships for different interconnect media                                               | 6          |

| 1.3 | Broad brush comparison of (\$US) costs for a WSI based product com-                                       |            |

|     | pared with the equivalent discrete die and board based product                                            | 12         |

| 2.1 | Cross section of Mosaic's silicon circuit board                                                           | 24         |

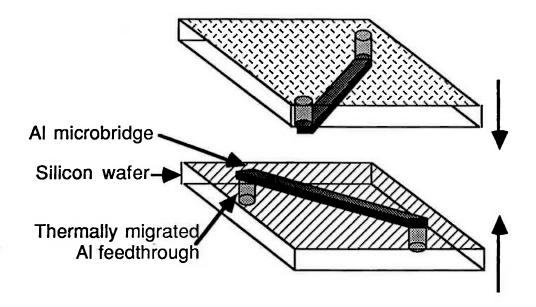

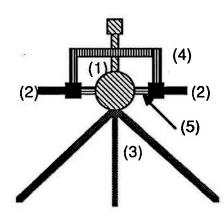

| 2.2 | Microbridge connector structure developed by Hughes                                                       | 29         |

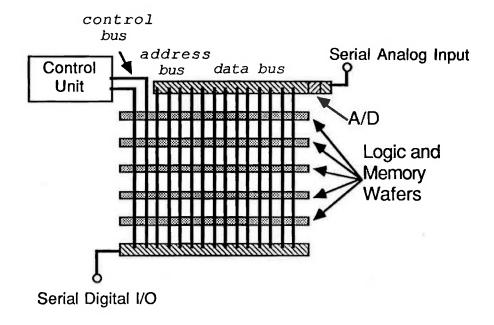

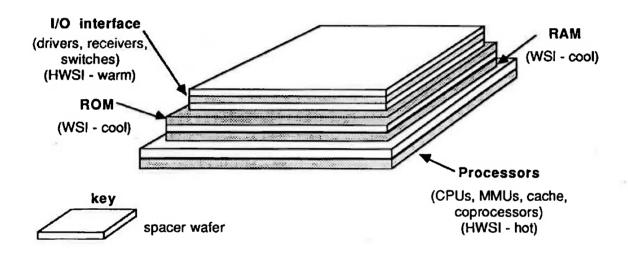

| 2.3 | Basic structure of Hughes 3D computer                                                                     | 30         |

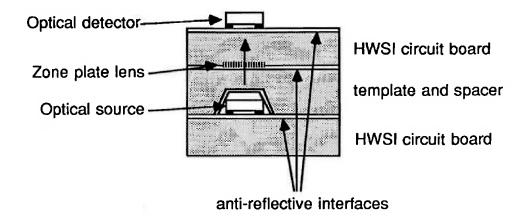

| 2.4 | Through the wafer free space optical interconnect                                                         | 31         |

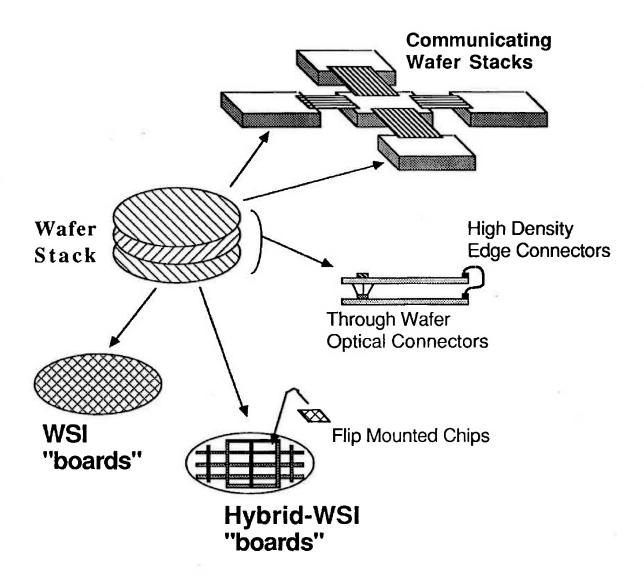

| 2.5 | Integrating technologies to form a wafer stack                                                            | <b>3</b> 2 |

| 2.6 | A future mesh-connected multicomputer                                                                     | 33         |

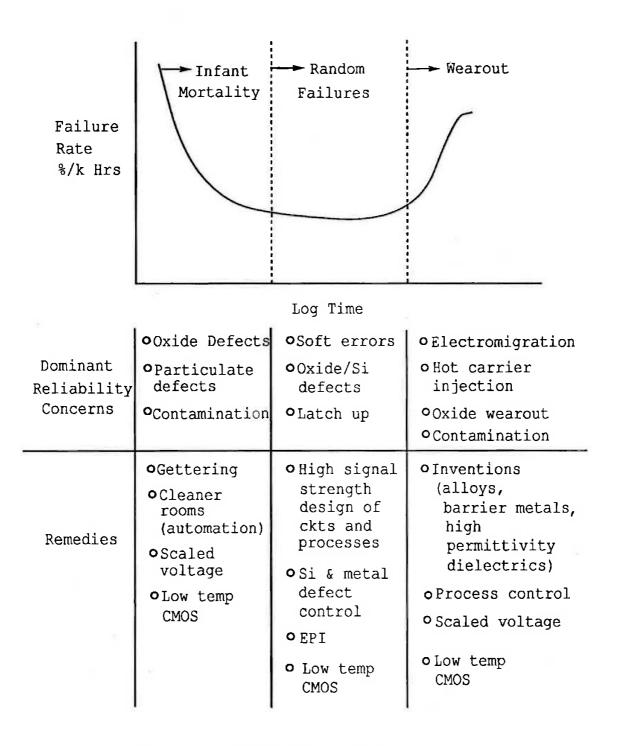

| 3.1 | Reliability failure rate bathtub curve                                                                    | 37         |

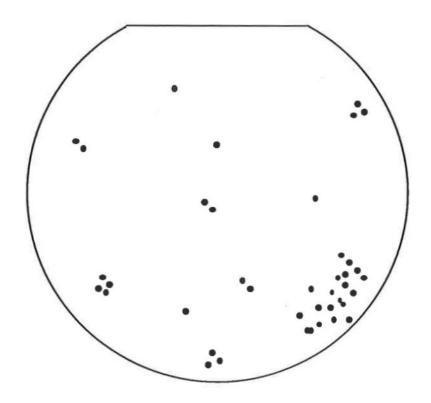

| 3.2 | Example of defect clustering on a wafer                                                                   | 39         |

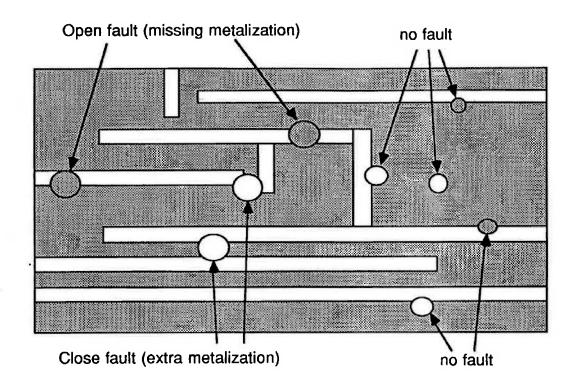

| 3.3 | Examples of photolithographic defects                                                                     | 55         |

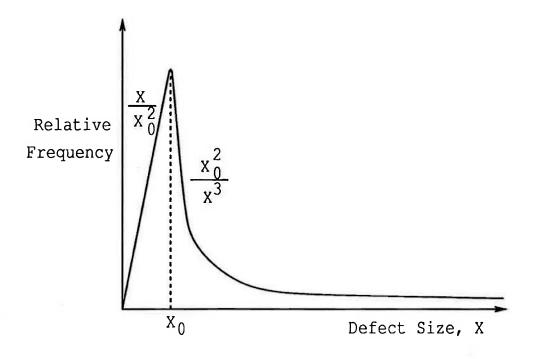

| 3.4 | Defect Size Distribution                                                                                  | 56         |

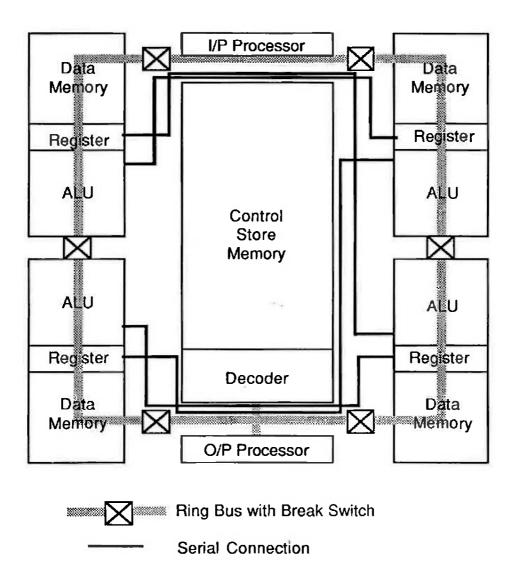

| 3.5 | Floorplan for the Transform and Filter Brick                                                              | 58         |

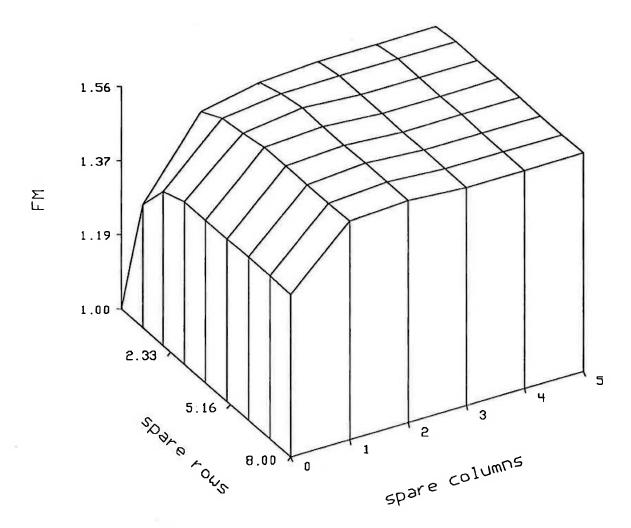

| 3.6 | Figures of Merit (FM) vs. the number of spare columns and rows                                            |            |

|     | in the control store, for the whole chip with parameters: $D_0 = 0.10$                                    |            |

|     | defects/mm <sup>2</sup> . $\alpha = 2$ . $A_{cell} = 0.55A_{mem}$ , $A_{col} = 0.19A_{mem}$ , $A_{row} =$ |            |

|     | $0.25A_{mem}$                                                                                             | 62         |

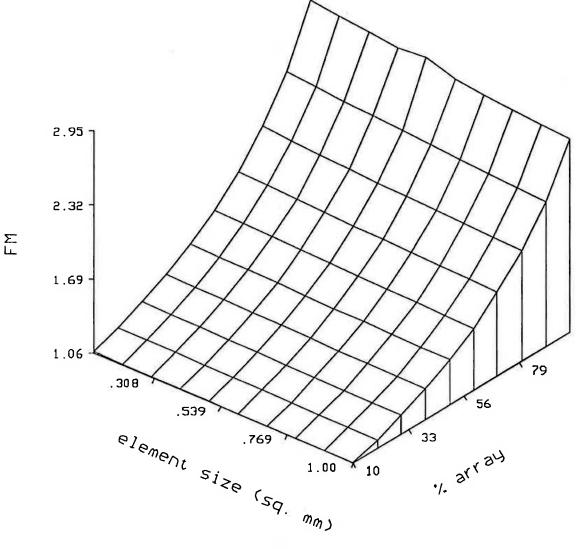

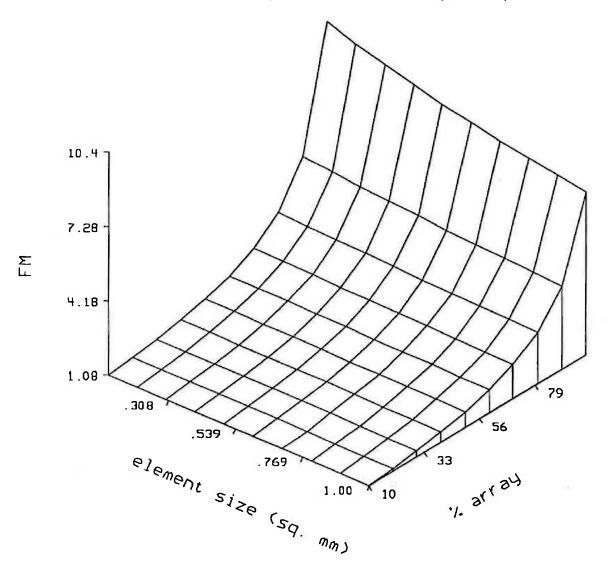

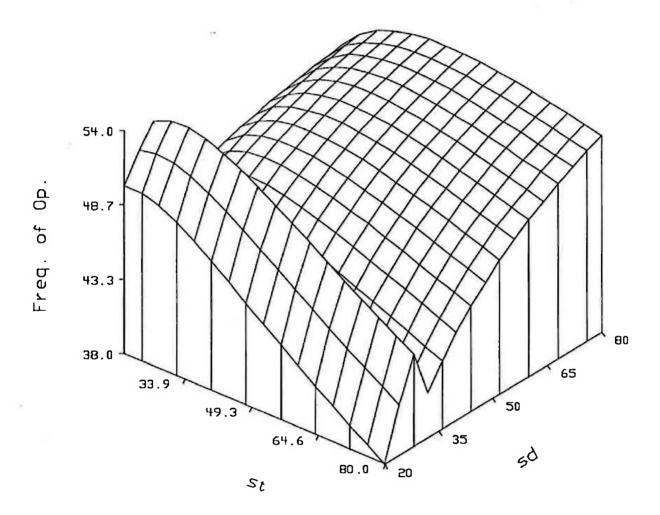

| 3.7 | Figure of Merit $FM$ vs. replicated element size, and the % of the                                        |            |

|     | chip area covered by the array containing this element. $(D_0 = 0.02)$                                    | Ŀ.         |

|     | defects/mm <sup>2</sup> )                                                                                 | 64         |

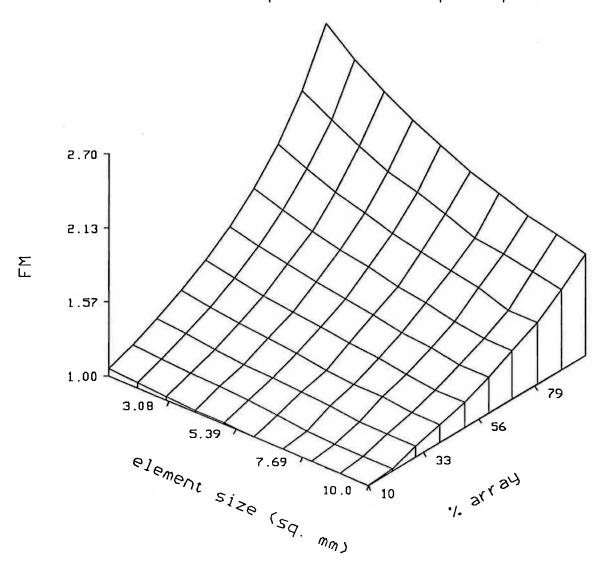

| 3.8 | Figure of Merit $FM$ vs. replicated element size, and the % of the                                        |            |

|     | chip area covered by the array containing this element. ( $D_0 = 0.02$                                    |            |

|     | defects/mm <sup>2</sup> and larger element size range)                                                    | 65         |

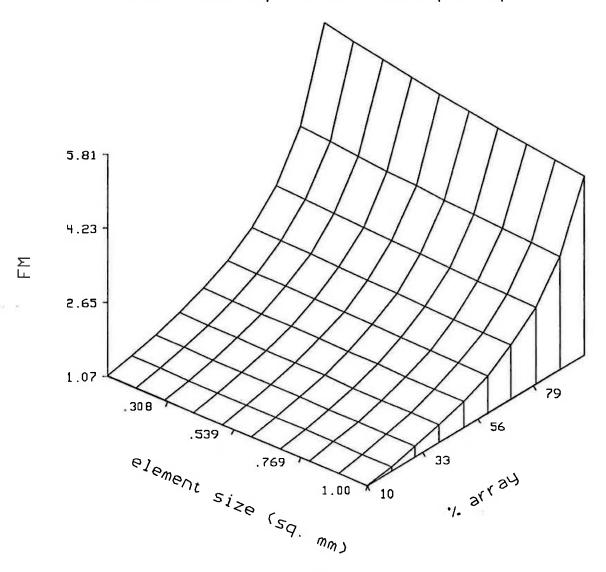

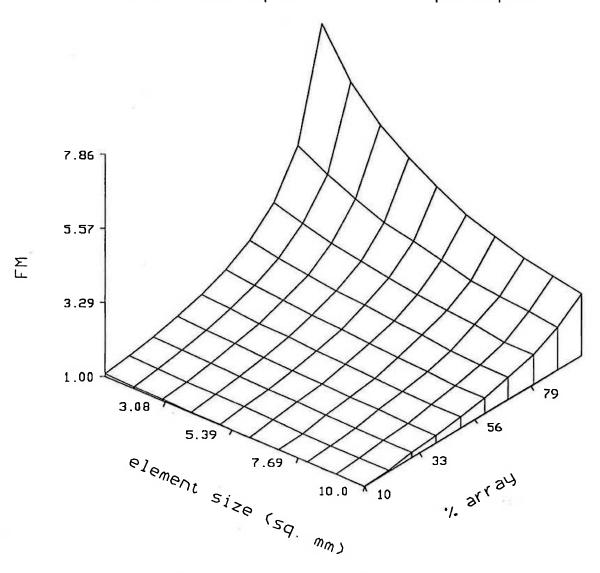

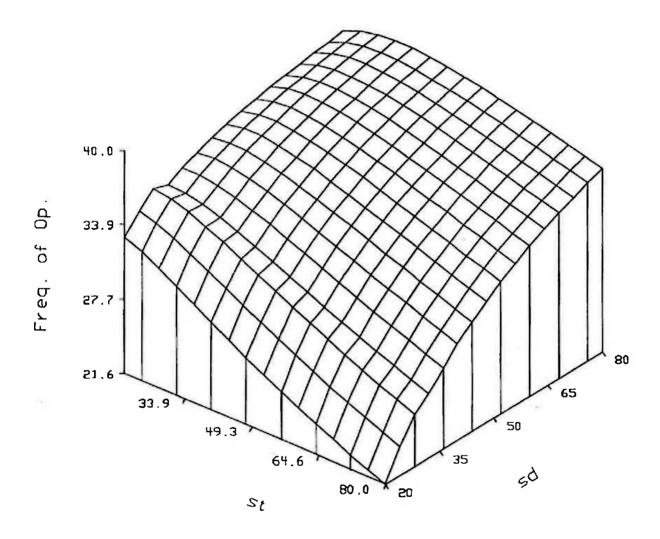

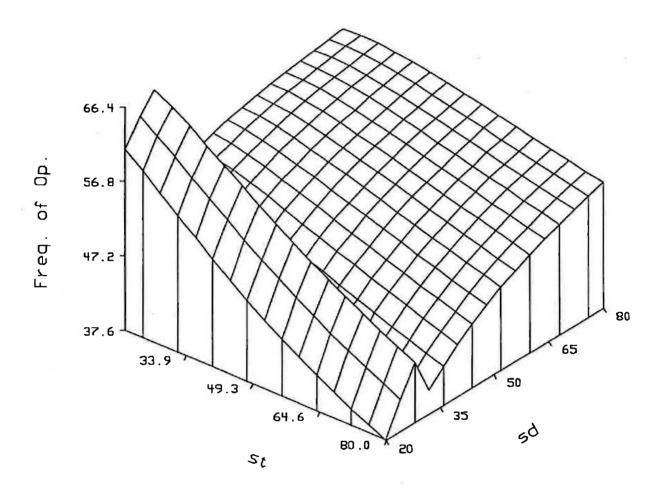

| 3.9  | Figure of Merit $FM$ vs. replicated element size, and the % of the             |             |

|------|--------------------------------------------------------------------------------|-------------|

|      | chip area covered by the array containing this element. ( $D_0 = 0.05$         |             |

|      | defects/mm <sup>2</sup> )                                                      | 66          |

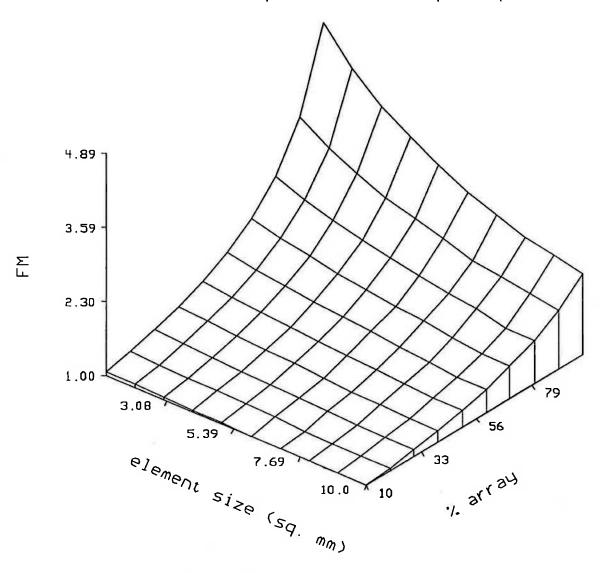

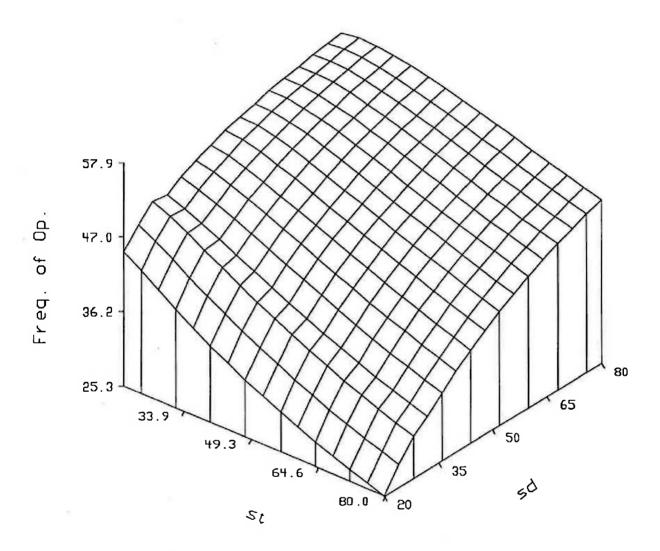

| 3.10 | Figure of Merit $FM$ vs. replicated element size, and the % of the             |             |

|      | chip area covered by the array containing this element. ( $D_0 = 0.05$         |             |

|      | defects/mm <sup>2</sup> and larger element size range)                         | 67          |

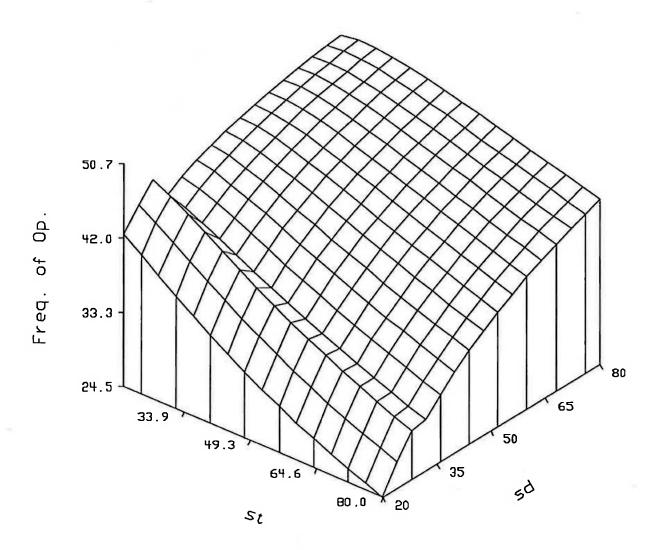

| 3.11 | Figure of Merit $FM$ vs. replicated element size, and the % of the             |             |

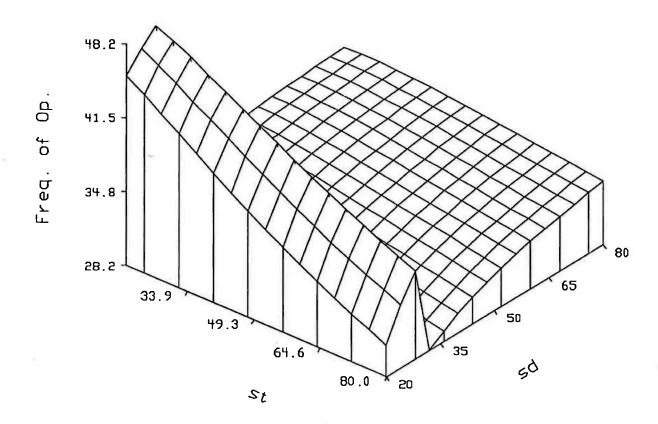

|      | chip area covered by the array containing this element. ( $D_0=0.10$           |             |

|      | defects/mm <sup>2</sup> )                                                      | 68          |

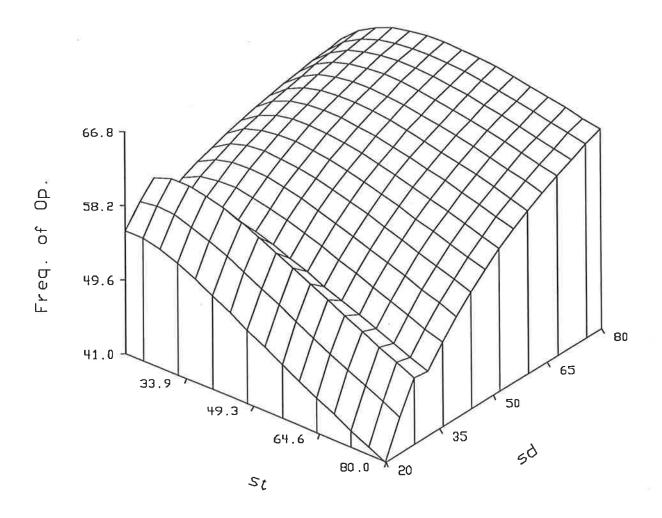

| 3.12 | Figure of Merit $FM$ vs. replicated element size, and the % of the             |             |

|      | chip area covered by the array containing this element. ( $D_0 = 0.10$         |             |

|      | defects/mm <sup>2</sup> and larger element size range)                         | 69          |

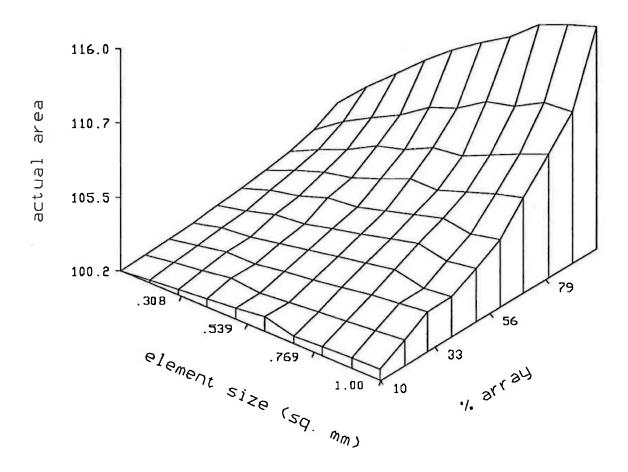

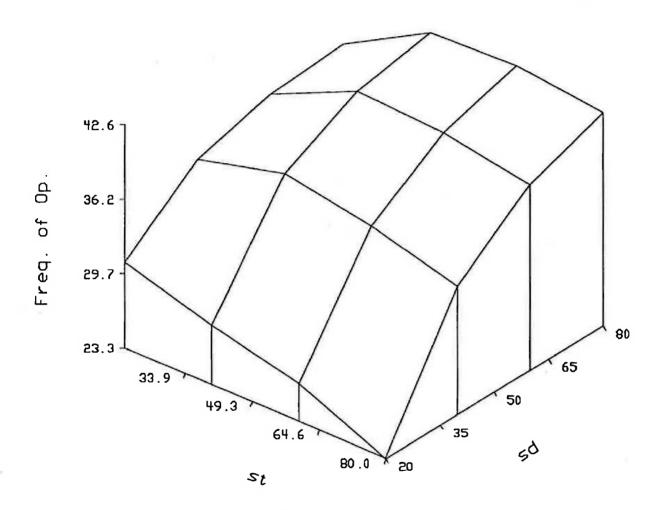

| 3.13 | Actual area required to achieve optimal Figures of Merit for $D_0=$            |             |

|      | 0.05 defects/mm <sup>2</sup> case                                              | 70          |

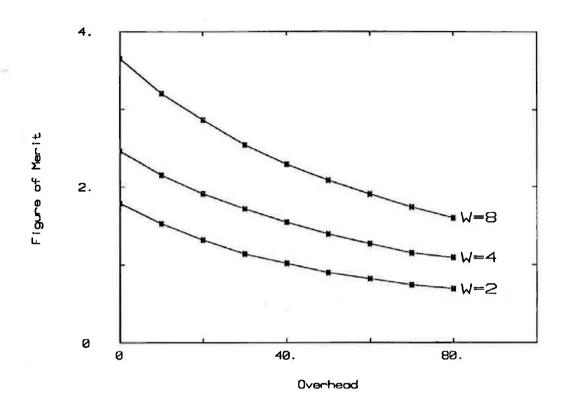

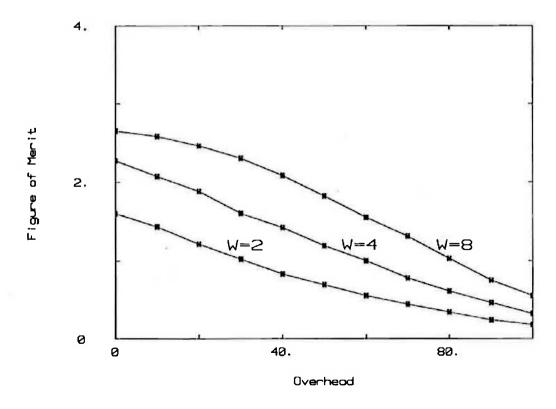

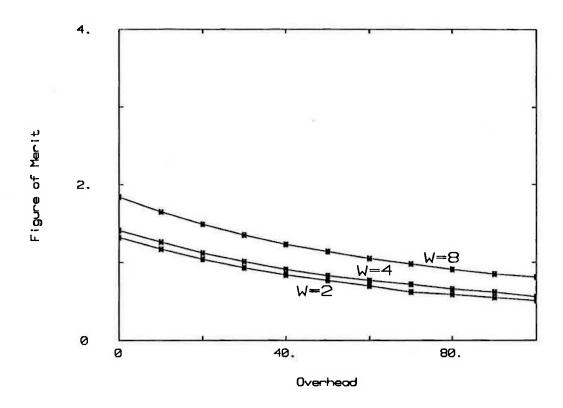

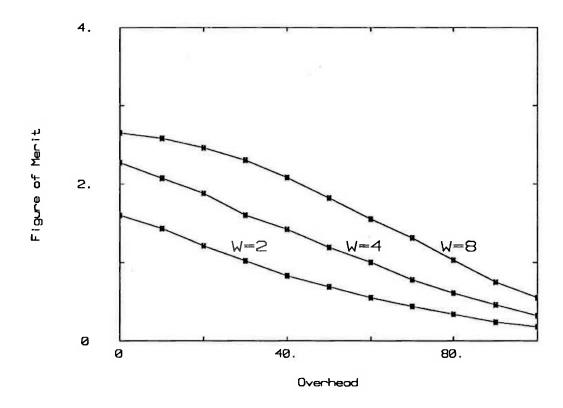

| 3.14 | Effect of partitioning on the $FM$ : Expanding area, $A_{PE}=50~\mathrm{mm^2}$ | 73          |

| 3.15 | Effect of partitioning on the $FM$ : Constant area, $A_{PE}=50~\mathrm{mm}^2$  | 73          |

| 3.16 | Effect of partitioning on the $FM$ : Expanding area, $A_{PE}=10~\mathrm{mm}^2$ | 74          |

| 3.17 | Effect of partitioning on the $FM$ : Constant area, $A_{PE}=10~\mathrm{mm}^2$  | 74          |

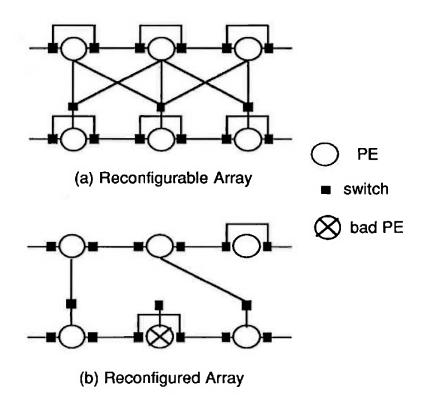

| 3.18 | Mesh array reconfiguration scheme showing (a) all the wiring, and (b)          |             |

|      | an example with faults                                                         | 78          |

| 3.19 | Contribution of wiring areas to yield areas                                    | 79          |

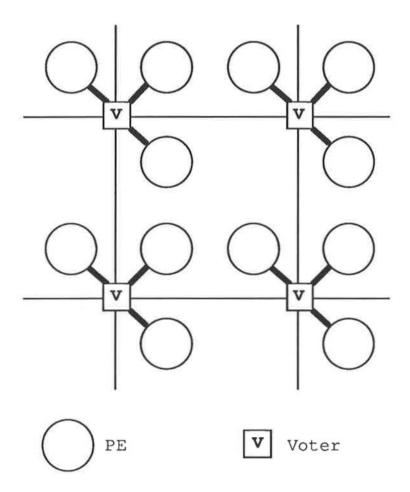

| 4.1  | TMR approach to implementing a fault tolerant array                            | 83          |

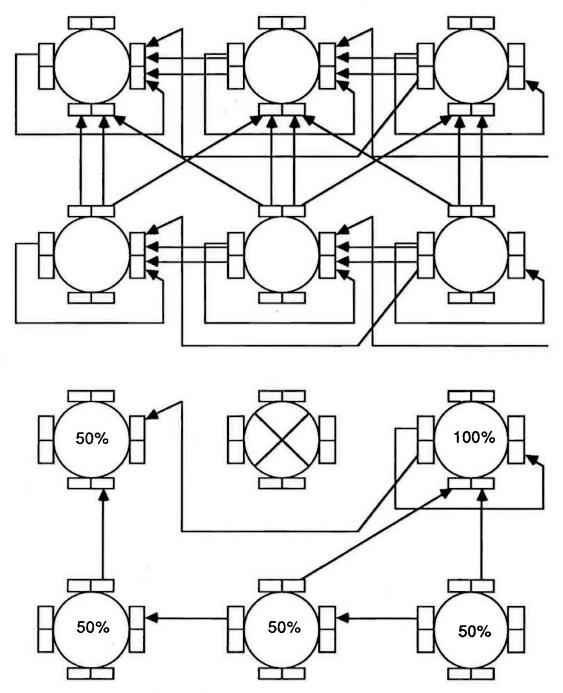

| 4.2  | A temporal redundancy approach to implementing a fault tolerant array.         | 85          |

| 4.3  | Example of a global redundancy approach to implementing a fault                |             |

|      | tolerant array.                                                                | 86          |

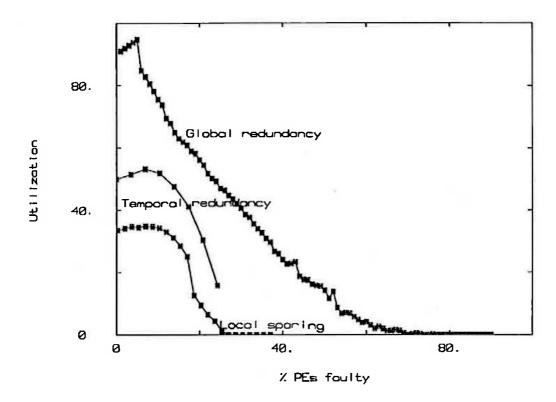

| 4.4  | Comparison of utilization for different redundancy approaches                  | 87          |

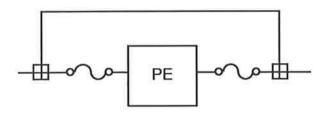

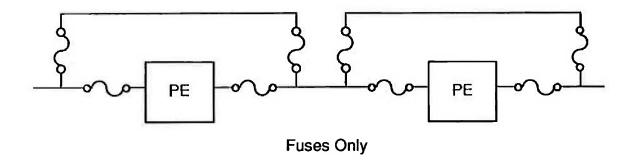

| 4.5  | Two approaches to using fuse/join techniques                                   | 89          |

| 4.6  | Comparison of fuse only and fuse/join techniques for linear arrays             | 90          |

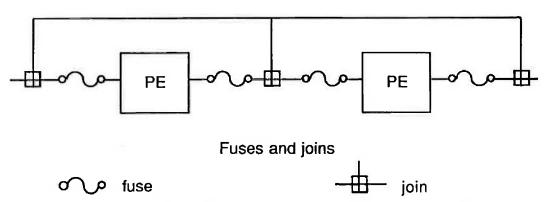

| 4.7  | Range of architecture topologies and their suitability for WSI                 | 92          |

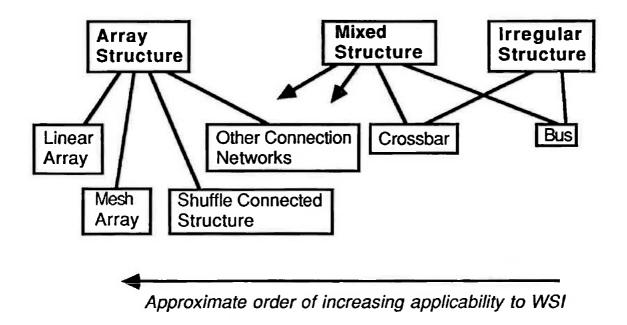

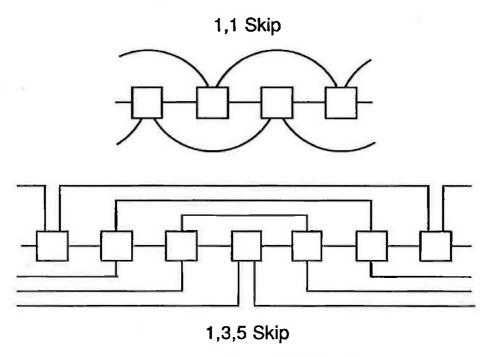

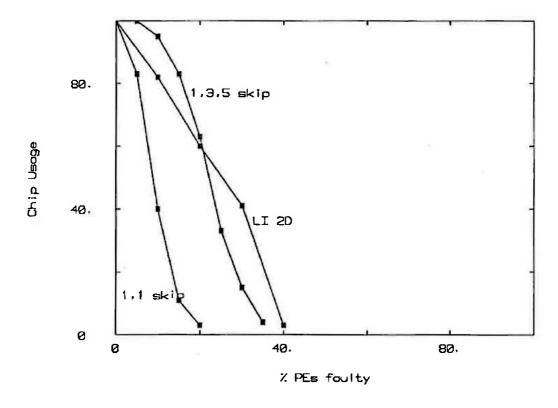

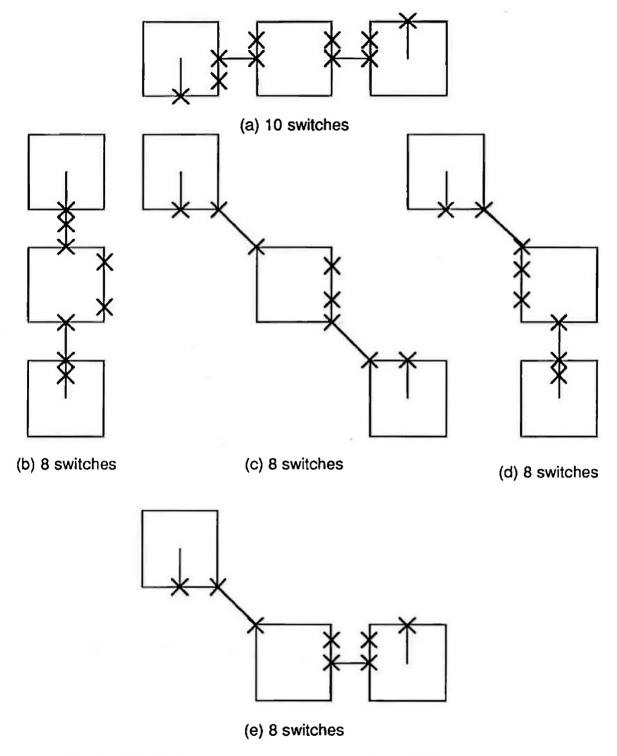

| 4.8  | Taxonomy of methods used to form fault tolerant linear arrays                  | 96          |

| 4.9  | Examples of LI chain schemes                                                   | 97          |

| 4.10 | Chip usage of LI linear schemes                                                | 97          |

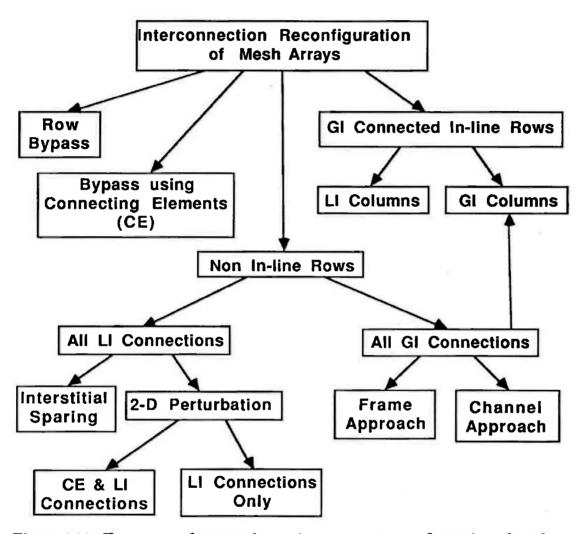

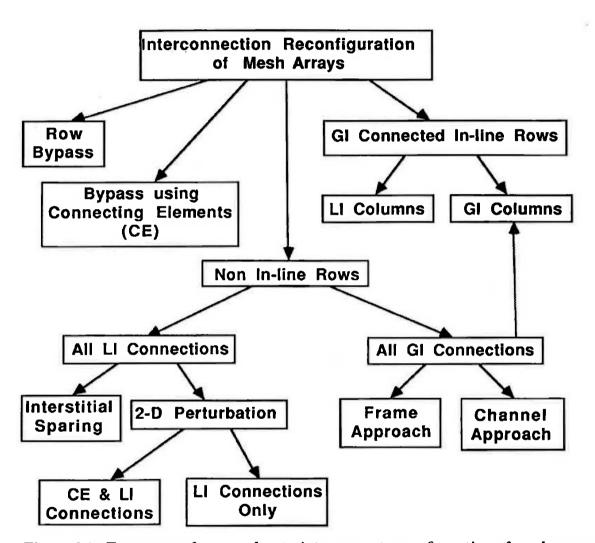

| 4.11 | Taxonomy of approaches to interconnect reconfiguration of mesh arrays.         | 99          |

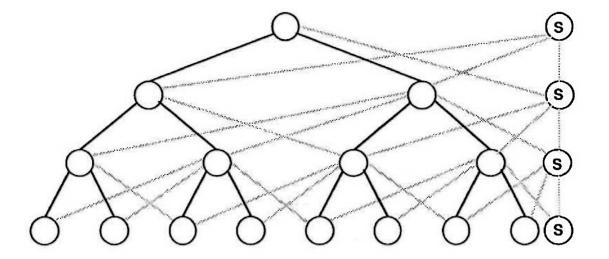

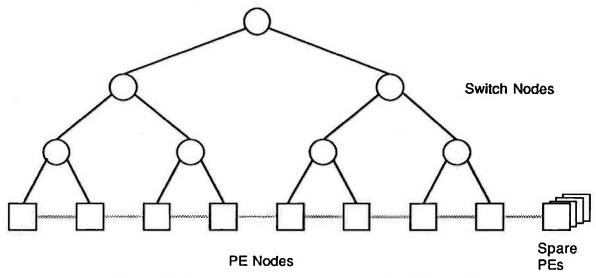

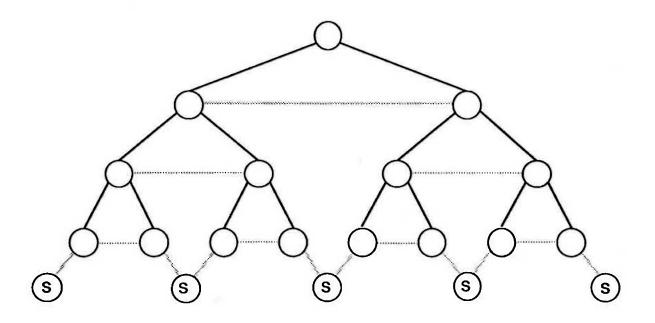

| 4.12 | First level redundancy approach to implementing fault tolerant trees 1         | 100         |

| 4.13 | Level redundancy on one (PE) level only                                        | l <b>01</b> |

| 4.14       | SOFT approach to fault tolerant trees                                      |

|------------|----------------------------------------------------------------------------|

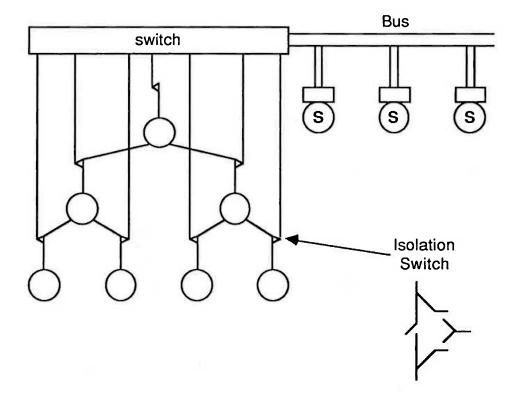

| 4.15       | Bussed sparing approach to tree fault-tolerance 102                        |

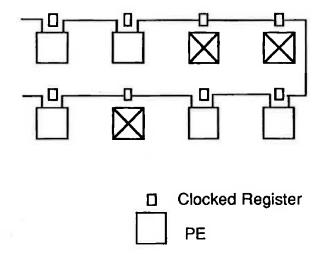

| 4.16       | Pipelining the interconnect can be used to maintain throughput 104         |

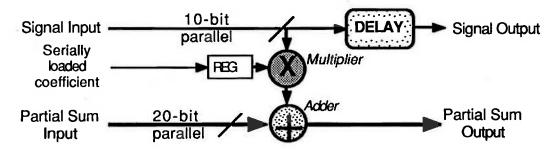

| 5.1        | FIR Filter Section with Fixed, Preloaded Coefficients for Testbed Array107 |

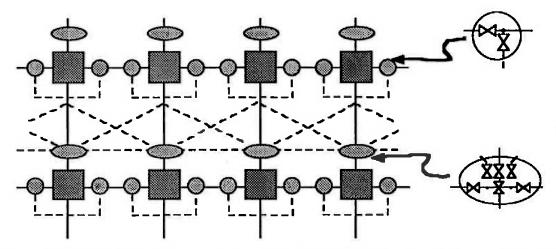

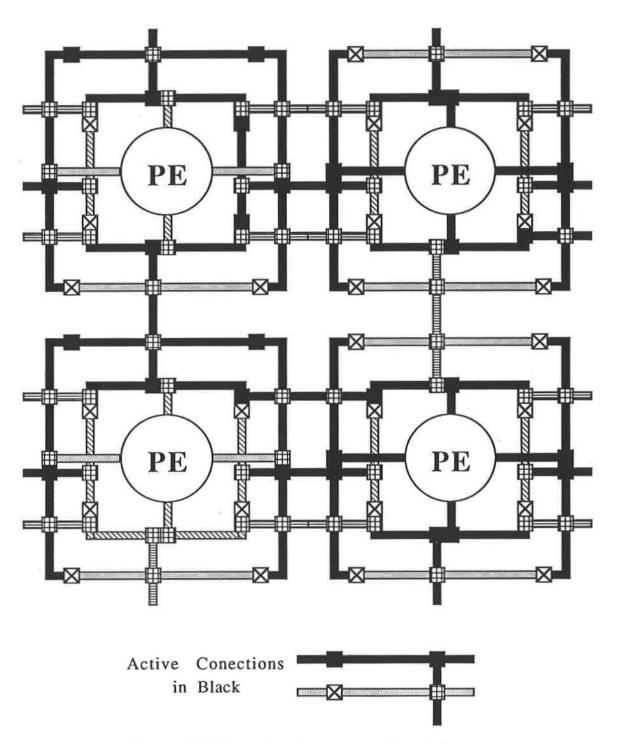

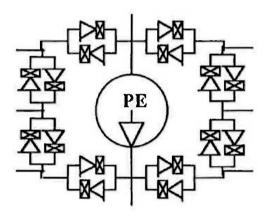

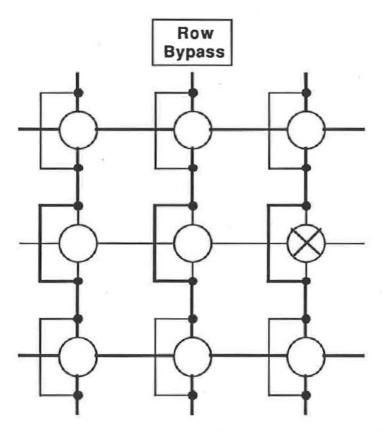

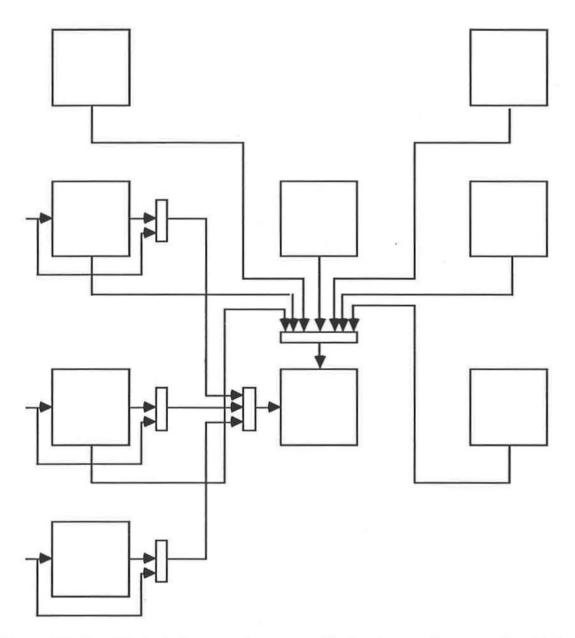

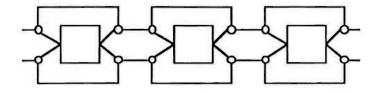

| 5.2        | Row-oriented reconfiguration (with pass-transistor based switches) 109     |

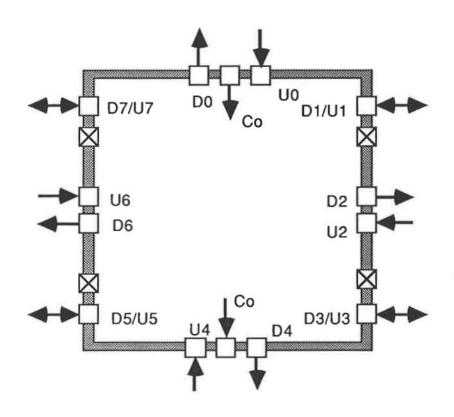

| 5.3        | Basic Outline of the Reconfiguration Scheme                                |

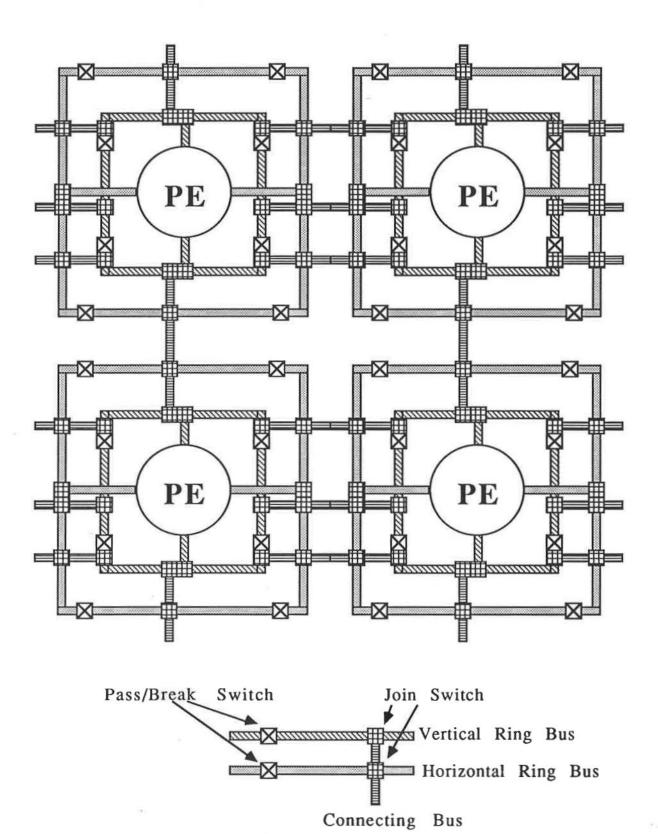

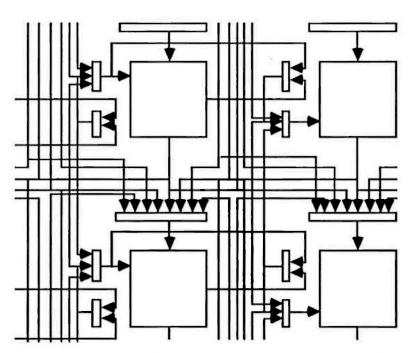

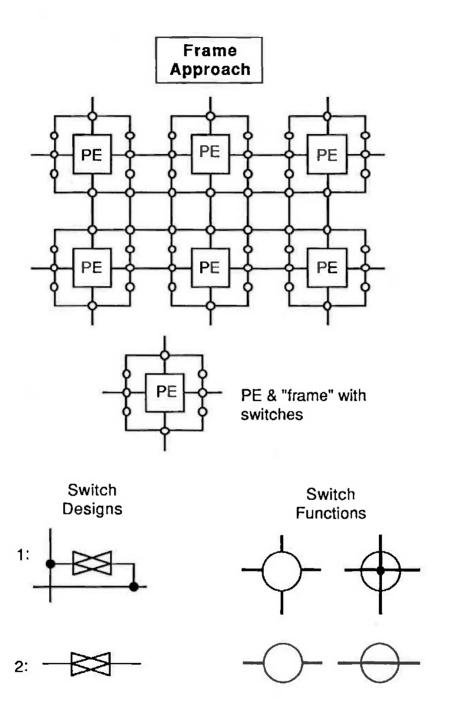

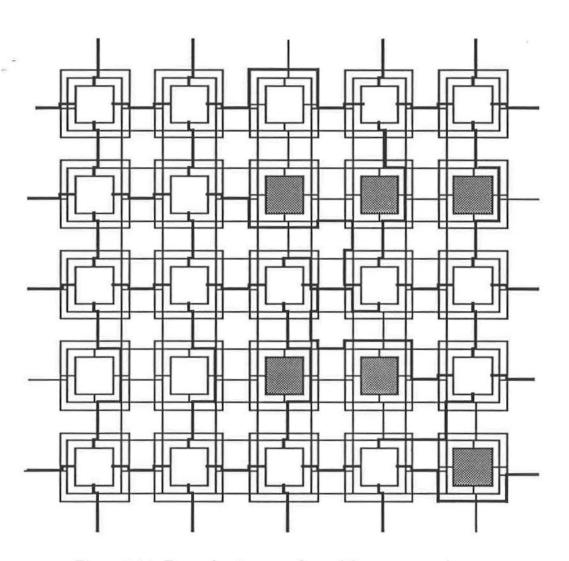

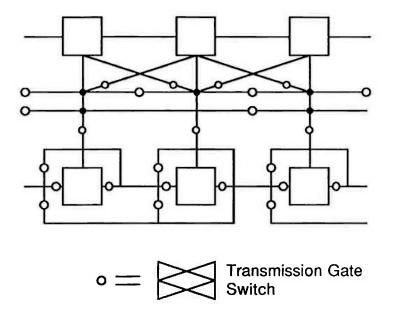

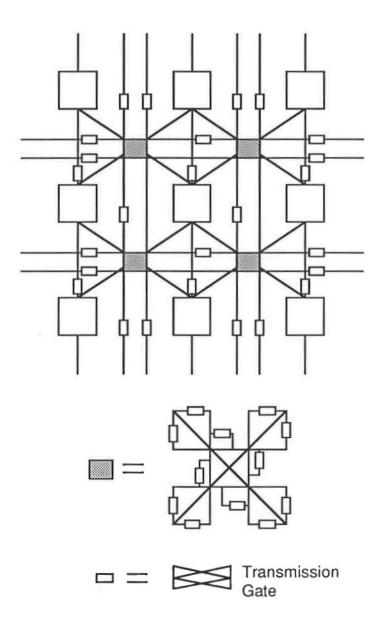

| 5.4        | Mesh-Connected Cell Array with reconfiguration Frame per Cell 112          |

| <b>5.5</b> | Examples of some reconfigured frames                                       |

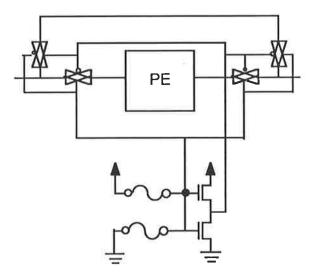

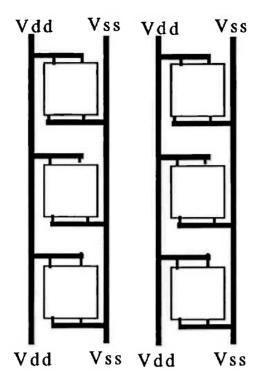

| 5.6        | Fault Tolerant Power Distribution                                          |

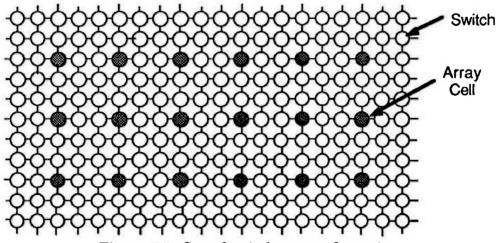

| 5.7        | Sea-of-switches reconfiguration                                            |

| 5.8        | Programmable Control of Reconfiguration State                              |

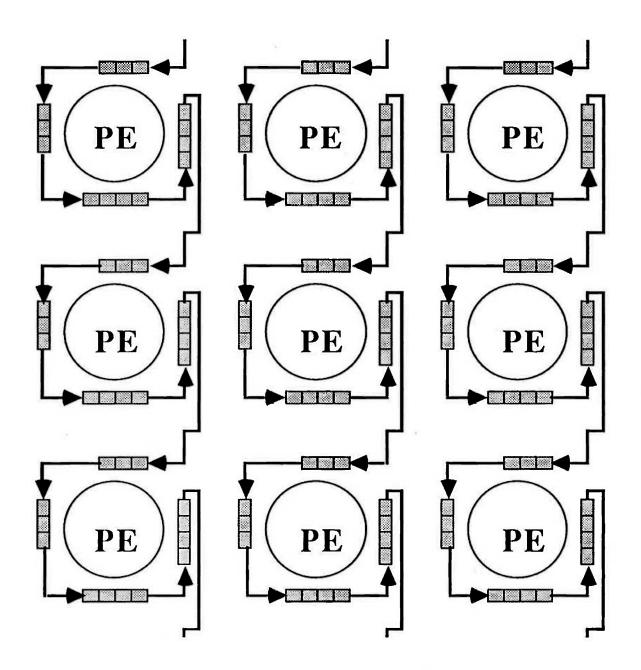

| 5.9        | Programming the Wafer-Scale Array                                          |

| 5.10       | Allowed vertical bus configurations (Figure 1 of 4)                        |

| 5.11       | Allowed vertical bus configurations (Figure 2 of 4)                        |

| 5.12       | Allowed vertical bus configurations (Figure 3 of 4)                        |

| 5.13       | Allowed vertical bus configurations (Figure 4 of 4)                        |

| 5.14       | Internal control signals                                                   |

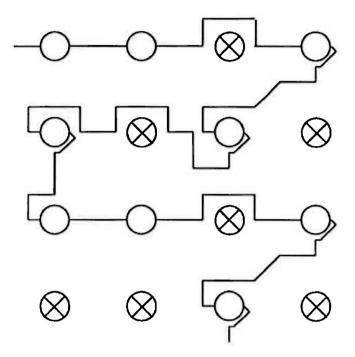

| 5.15       | Example of a configured linear array                                       |

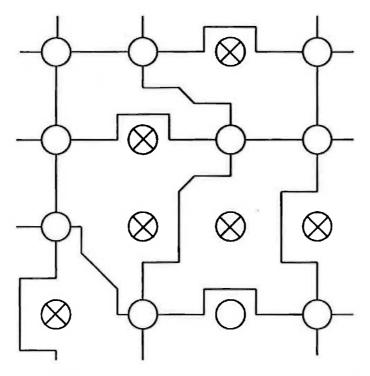

| 5.16       | Example of a configured mesh connected array                               |

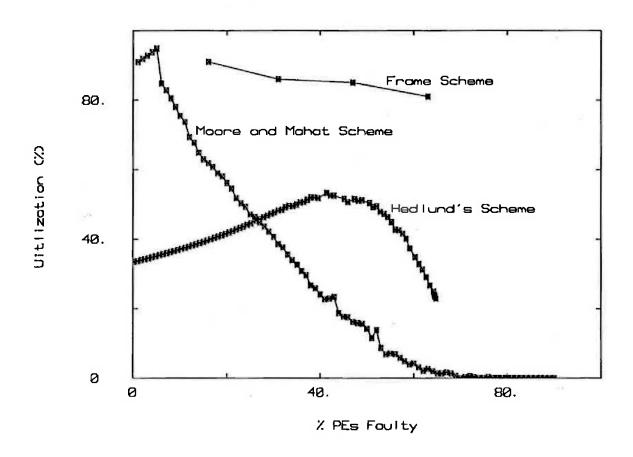

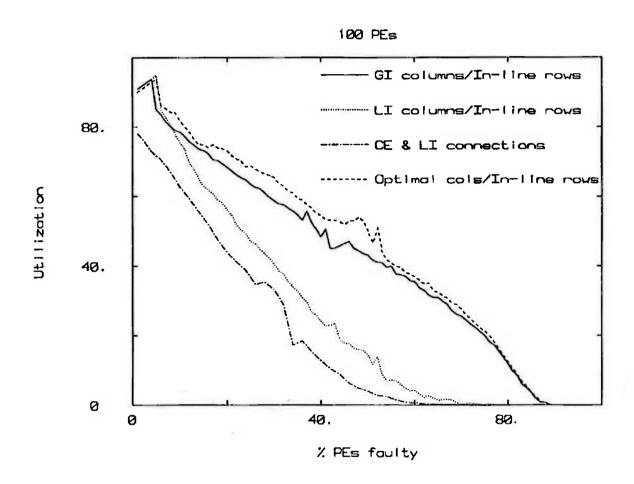

| 5.17       | Utilization vs. Cell Fault Probability for Frame and Other Schemes         |

|            | Above                                                                      |

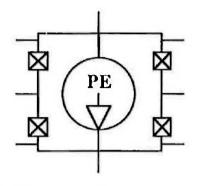

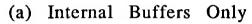

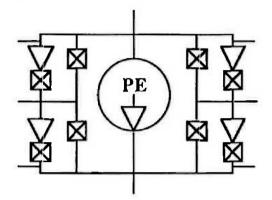

| 5.18       | Unbuffered and Various Buffered Frame Designs                              |

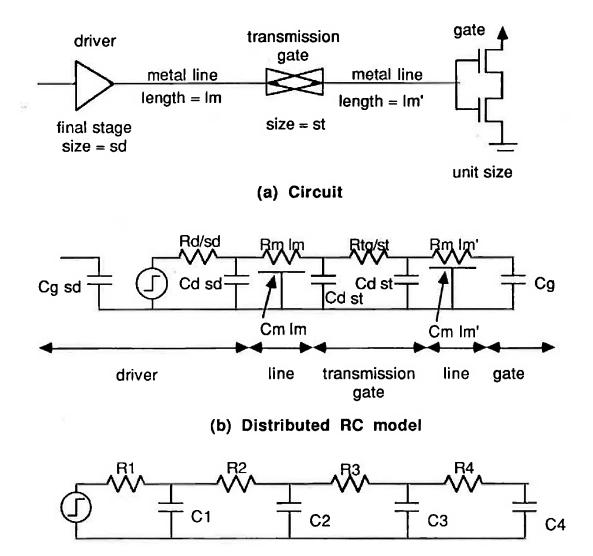

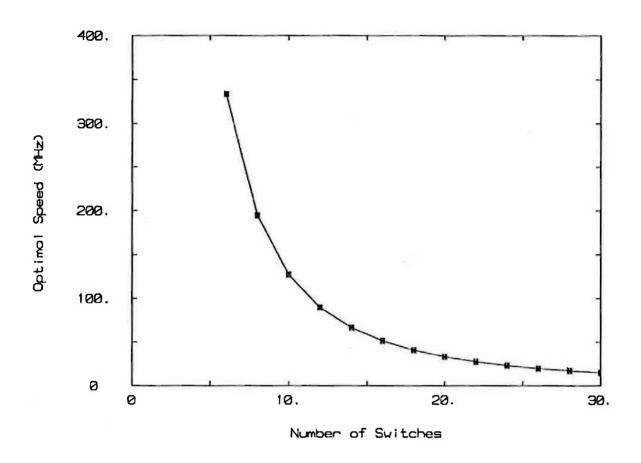

| 5.19       | A length of reconfigurable interconnect and its equivalent RC model $130$  |

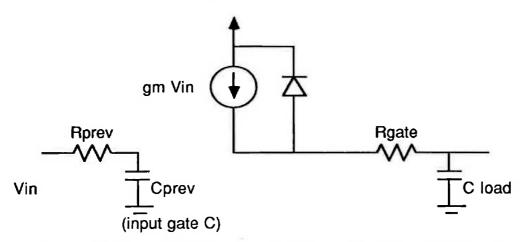

| 5.20       | Modified circuit model for a gate with a rising input                      |

| 5.21       | Derivation of worst case delay (Case (a)) for 1 PE bypass                  |

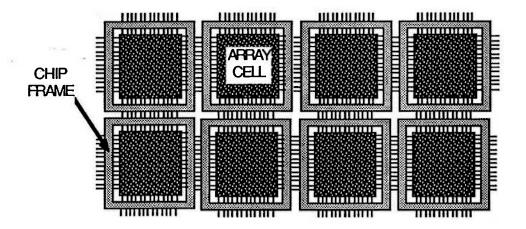

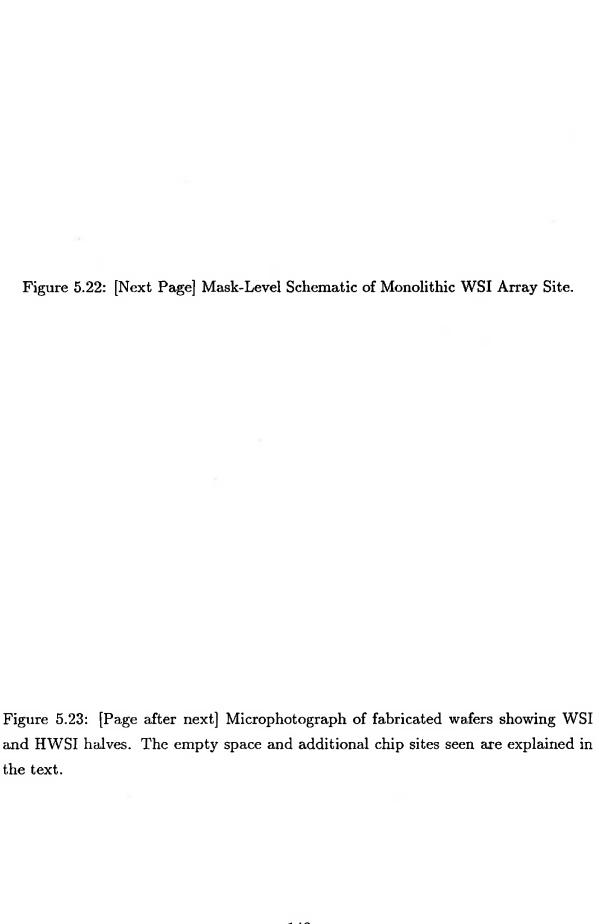

| 5.22       | [Next Page] Mask-Level Schematic of Monolithic WSI Array Site 140          |

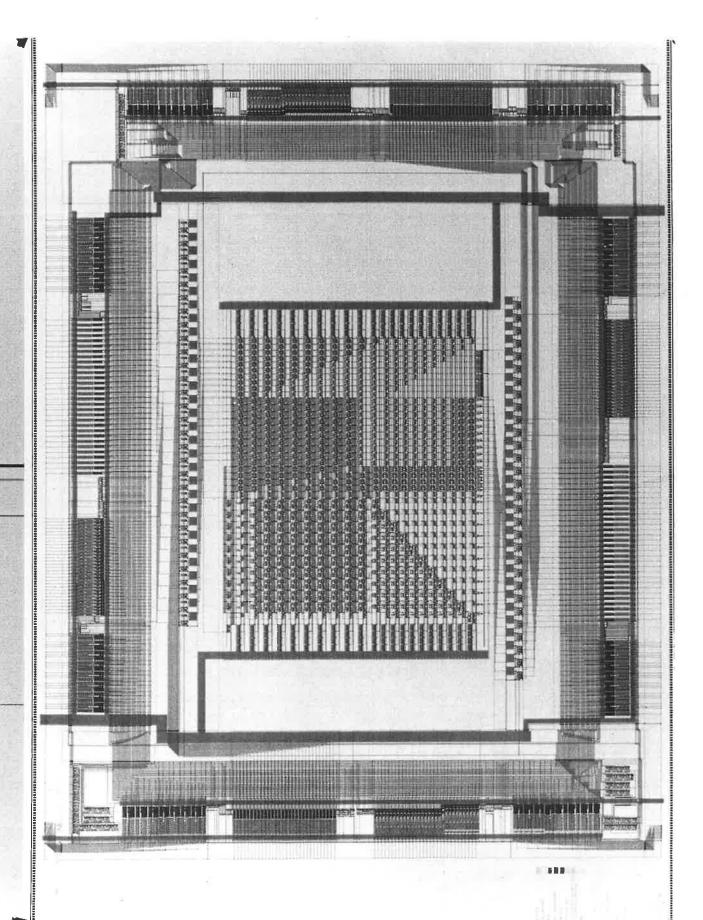

| 5.23       | [Page after next] Microphotograph of fabricated wafers showing WSI         |

|            | and HWSI halves. The empty space and additional chip sites seen are        |

|            | explained in the text                                                      |

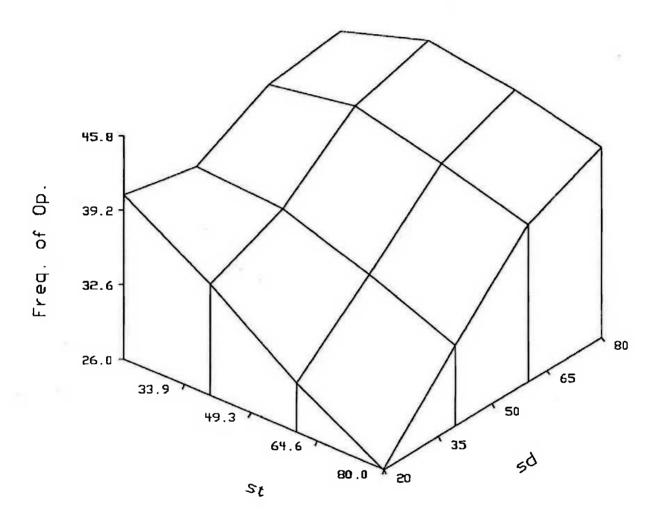

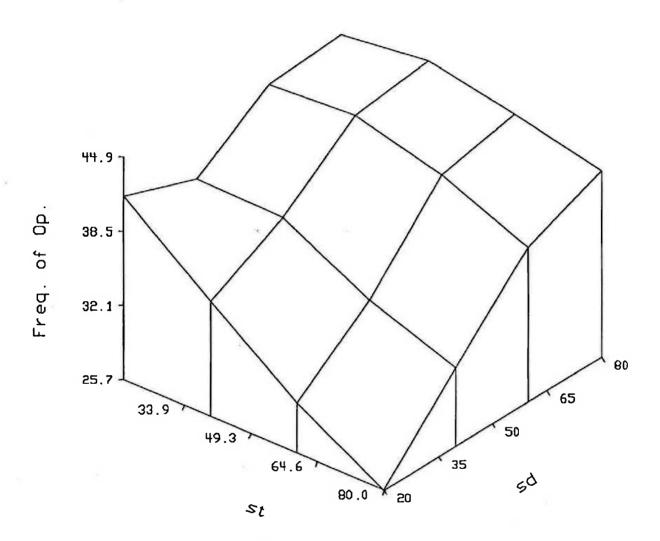

| 5.24       | Speed vs. driver and transmission gate size. Case (1) Non buffered.        |

|            | Simple RC model                                                            |

| 5.25       | Speed vs. driver and transmission gate size. Case (1) Non buffered.        |

|            | Complex RC model                                                           |

| 5.26       | Speed vs. driver and transmission gate size. Case (2) Bypass Drivers-      |

|            | Simple RC model                                                            |

| 5.27 | Speed vs. driver and transmission gate size. Case (2) Bypass drivers.     |

|------|---------------------------------------------------------------------------|

|      | Complex RC model                                                          |

| 5.28 | Speed vs. driver and transmission gate size. Case (3) Inter-PE buffers.   |

|      | Simple RC model                                                           |

| 5.29 | Speed vs. driver and transmission gate size. Case (3) Inter-PE buffers.   |

|      | Complex RC model                                                          |

| 5.30 | Speed vs. driver and transmission gate size. Case (4) Fully buffered.     |

|      | Simple RC model                                                           |

| 5.31 | Speed vs. driver and transmission gate size. Case (4) Fully buffered.     |

|      | Complex RC model                                                          |

| 5.32 | Speed vs. driver and transmission gate size. Case (1) Non-buffered.       |

|      | ADVICE results                                                            |

| 5.33 | Speed vs. driver and transmission gate size. Case (2) Bypass drivers.     |

|      | ADVICE results                                                            |

| 5.34 | Speed vs. driver and transmission gate size. Case (3) Inter-PE buffers.   |

|      | ADVICE results                                                            |

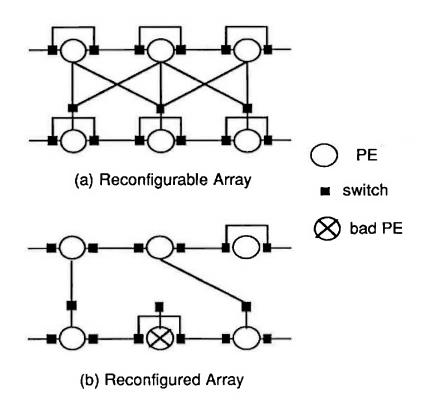

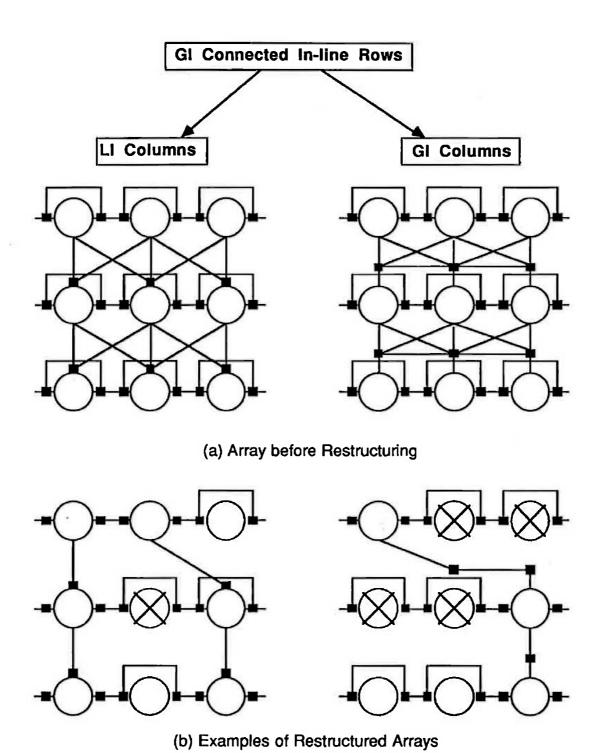

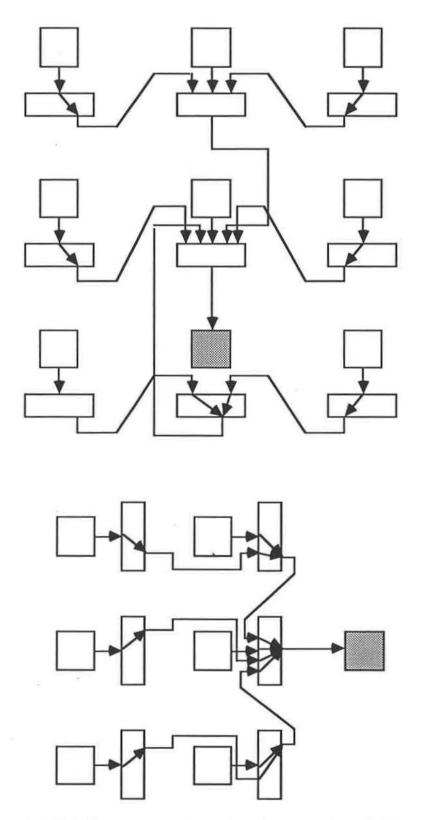

| 6.1  | Taxonomy of approaches to interconnect reconfiguration of mesh arrays.155 |

| 6.2  | Example of a reconfiguration scheme using row bypass 156                  |

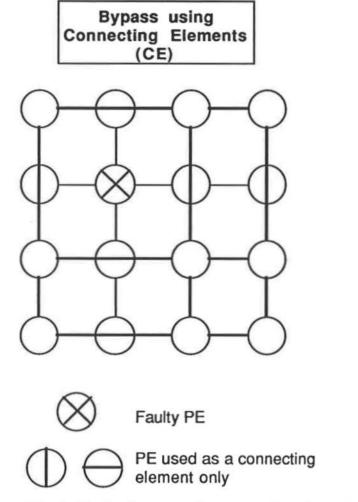

| 6.3  | Achieving bypass using connecting elements 157                            |

| 6.4  | Approaches to bypassing within rows, combined with column steering. 159   |

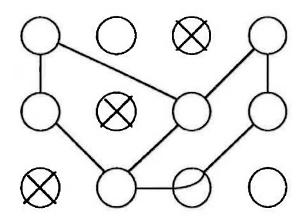

| 6.5  | An example of a 2-D perturbation scheme based on LI and CE switches.160   |

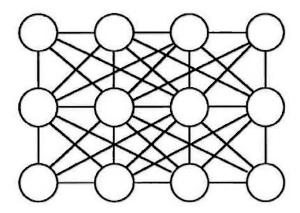

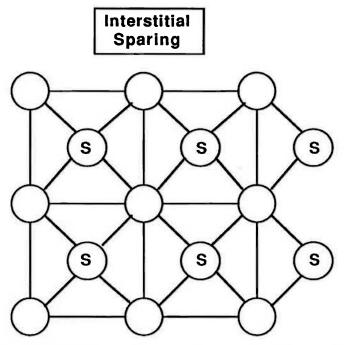

| 6.6  | Interstitial redundancy scheme using LI connections only 161              |

| 6.7  | Schematic Layout of direct-reconfiguration structure. (reproduced         |

|      | from [Sami and Stefanelli, 1986] (c)IEEE)                                 |

| 6.8  | Possible logical connections to a cell, showing employment of multi-      |

|      | plexor structures                                                         |

| 6.9  | Neighbour connections allowed using switched LI connections 164           |

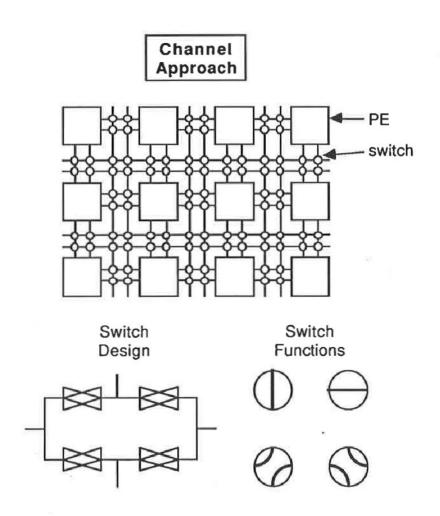

| 6.10 | Channel approach to fault tolerant mesh arrays                            |

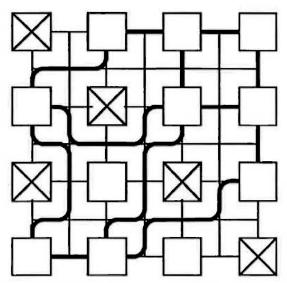

| 6.11 | Example of a reconfigured array using the channel approach (single        |

|      | channel width.)                                                           |

| 6.12 | Example of a reconfigured array using the channel approach (double        |

|      | channel width.)                                                           |

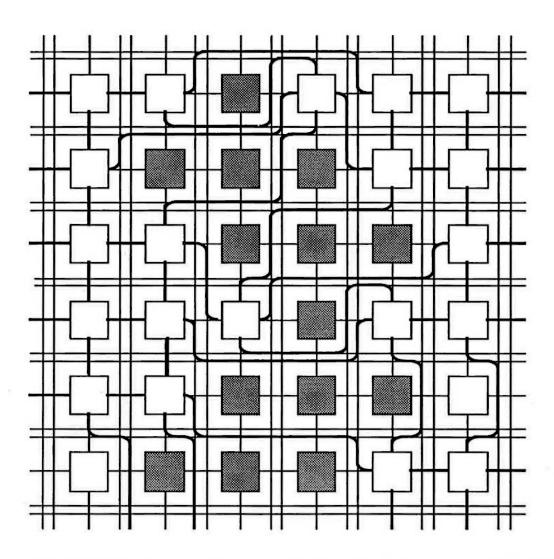

| 6.13 | Frame approach to all-GI connected array reconfiguration                  |

| 6.14 | Example of a reconfigured frame approach array                            |

| 6.15 | Comparison of the in-line row schemes and a combined CE/LI scheme. 171    |

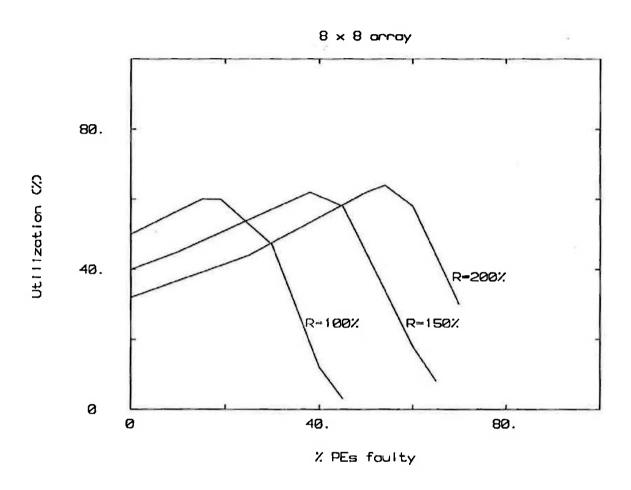

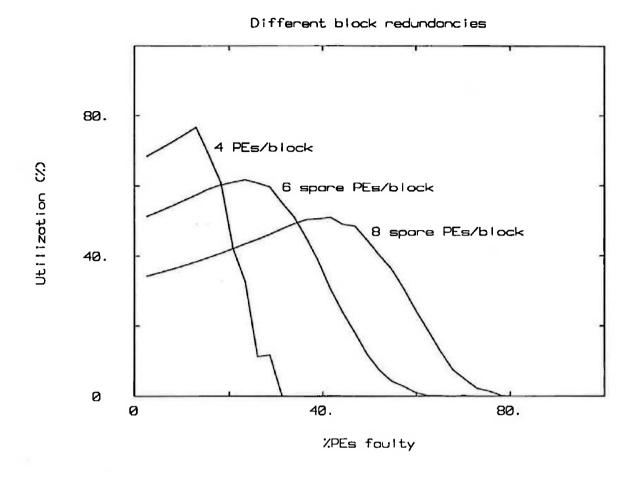

| 6.16 | Utilization of Interstitial Redundancy. $R$ is the level of redundancy 172      |

|------|---------------------------------------------------------------------------------|

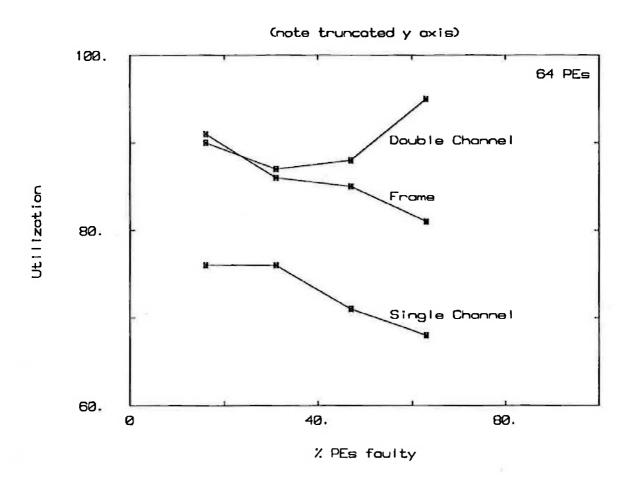

| 6.17 | Utilization comparison of different all-GI connected approaches 174             |

| 6.18 | Utilization vs. % of PEs faulty for a number of variations on Hedlund's         |

|      | hierarchical scheme. The labels refer to the number of PEs that are             |

|      | considered spare in each block of 12 PEs                                        |

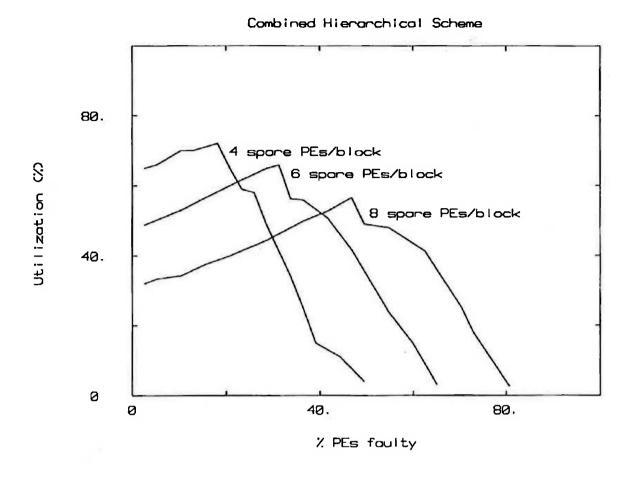

| 6.19 | Utilization achieved by combining the hierarchical approach with the            |

|      | GI-column/in-line row reconfiguration scheme for the blocks 176                 |

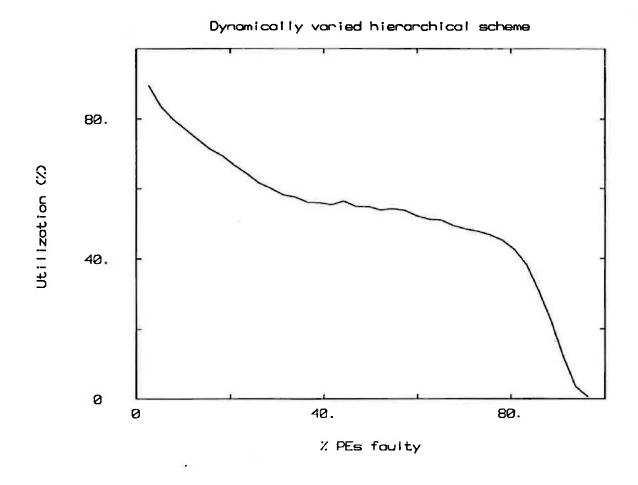

| 6.20 | Utilization of hierarchical scheme using varied width columns 177               |

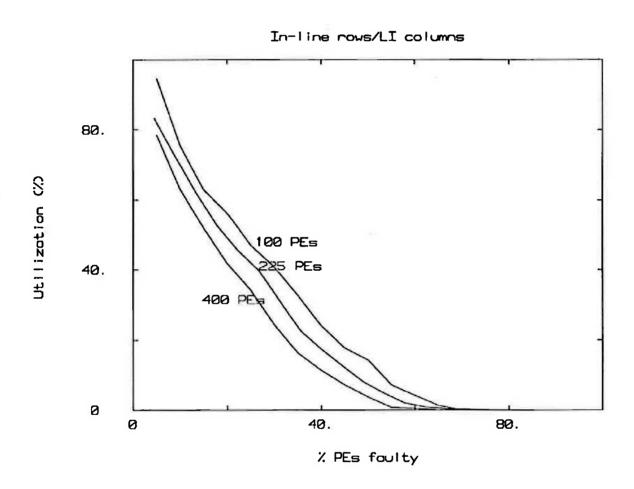

| 6.21 | Effect of array size on utilization of in-line rows/LI columns scheme 179       |

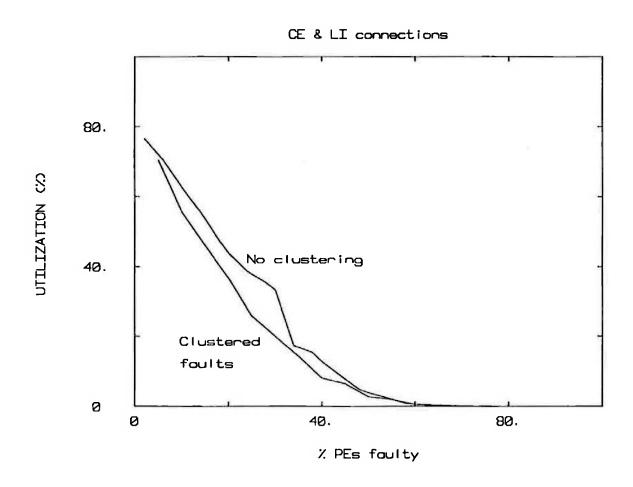

| 6.22 | Utilization of the CE & LI connections only scheme under assumptions            |

|      | of clustering and no clustering                                                 |

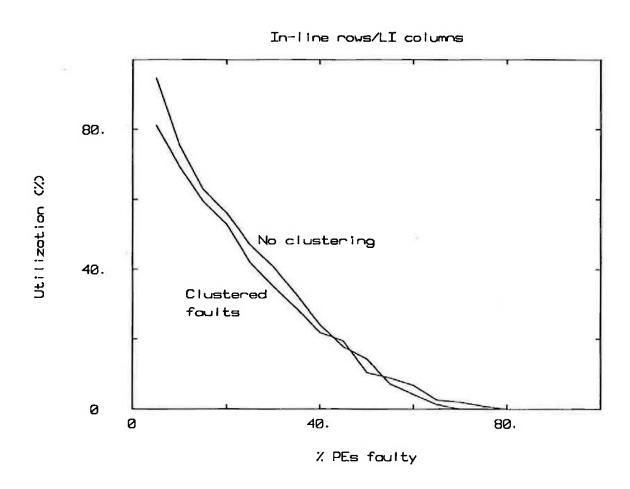

| 6.23 | Utilization of the in-line rows/LI columns scheme under assumptions             |

|      | of clustering and no clustering                                                 |

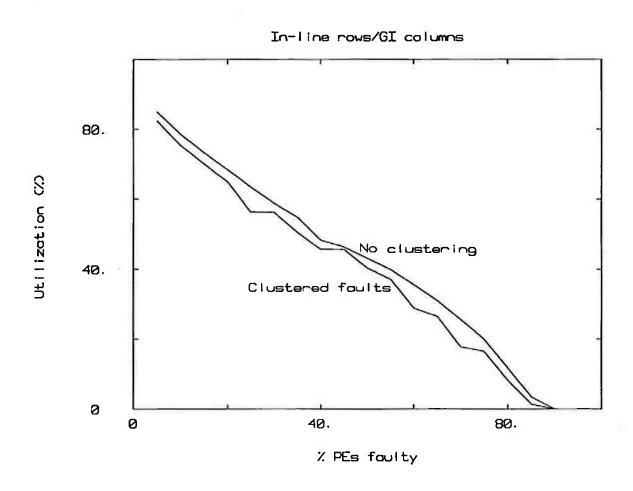

| 6.24 | Utilization of the in-line rows/GI columns scheme under assumptions             |

|      | of clustering and no clustering                                                 |

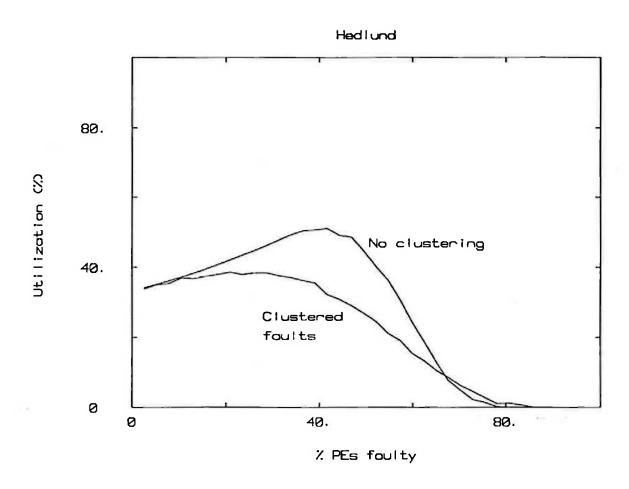

| 6.25 | Utilization of Hedlund's scheme under assumptions of clustering and             |

|      | no clustering                                                                   |

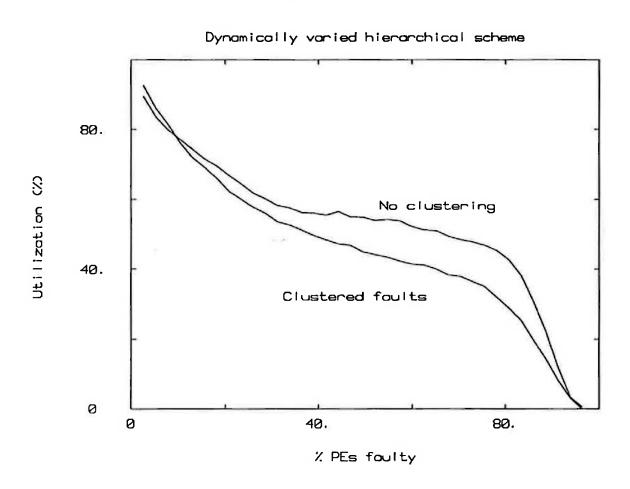

| 6.26 | Utilization of the dynamically varied block size hierarchical scheme            |

|      | under assumptions of clustering and no clustering                               |

| 6.27 | Utilization of all-GI schemes under assumptions of clustering and no            |

|      | clustering                                                                      |

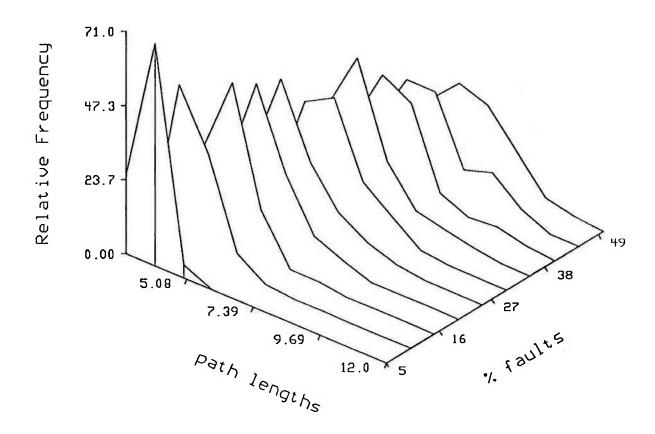

| 6.28 | Relative frequencies of maximum switch lengths, in terms of number              |

|      | of switches in that path for the in-line rows/GI columns scheme. The            |

|      | raw array consisted of 100 PEs                                                  |

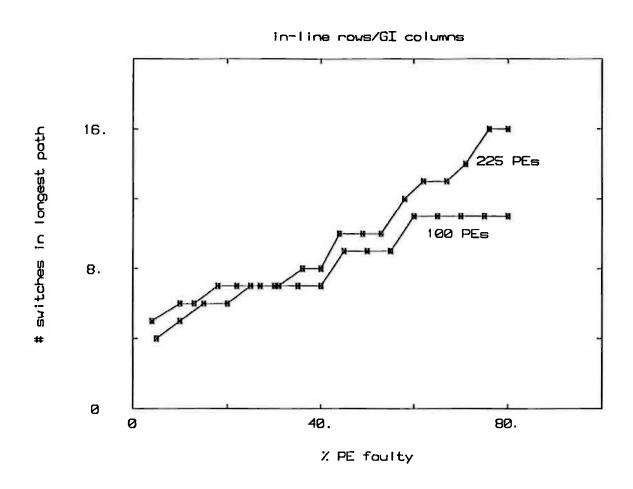

| 6.29 | Number of switches in in-line rows/GI columns scheme for a number               |

|      | of array sizes                                                                  |

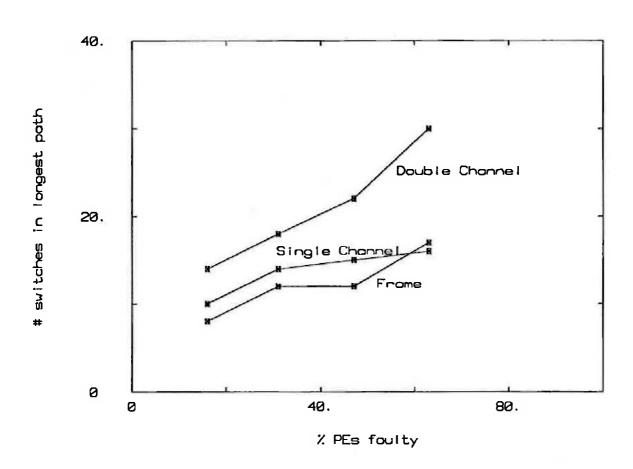

| 6.30 | Number of switches in longest path for all-GI schemes                           |

| 6.31 | Number of switches in longest path for all-GI schemes – clustered faults. $192$ |

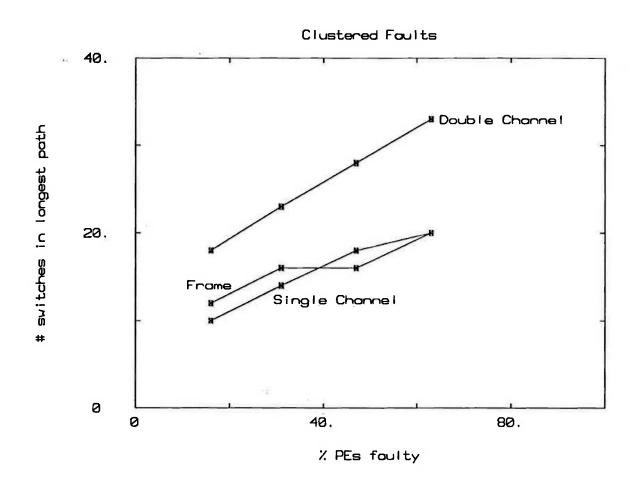

| 6.32 | A length of reconfigurable interconnect and its equivalent RC model 194         |

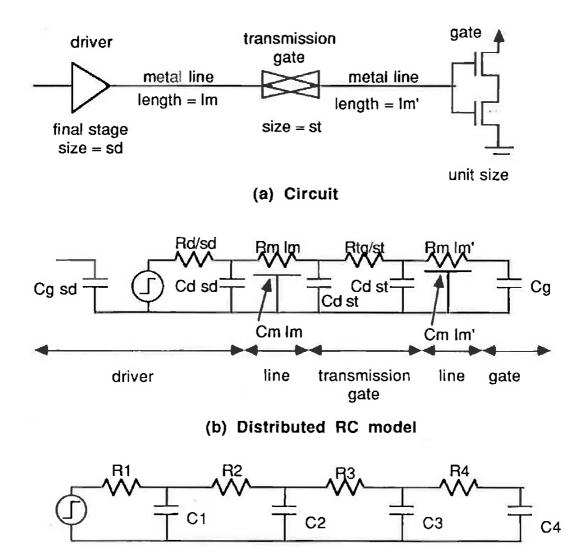

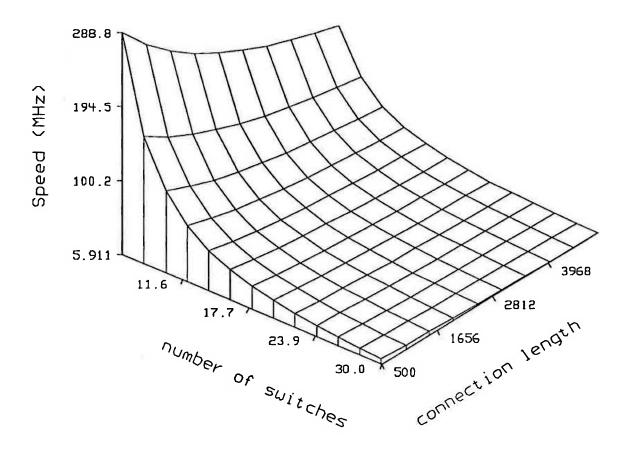

| 6.33 | Optimum communications speed for different switch numbers and                   |

|      | inter-switch wiring distances                                                   |

| 6.34 | Communications speed for different switch numbers and inter-switch              |

|      | wiring distances with the switch size set to $S=10.$                            |

| 6.35 | Approximate speed comparison of different redundancy approaches 198             |

| 6.36 | Improving in-line row schemes' effectiveness by making the row recon-           |

|      | figuration wiring itself defect tolerant                                        |

| 6.37 | GI columns/in-line rows scheme modification to improve speed 212     |

|------|----------------------------------------------------------------------|

| 6.38 | Vertical connections for an increased speed all-GI scheme. The hori- |

|      | zontal connections are identical in nature                           |

# List of Tables

| 1.1 | Comparison of Packages Figures of Merit                              |

|-----|----------------------------------------------------------------------|

| 2.1 | TRW's superchip set                                                  |

| 3.1 | Yield formula for different defect density distributions 41          |

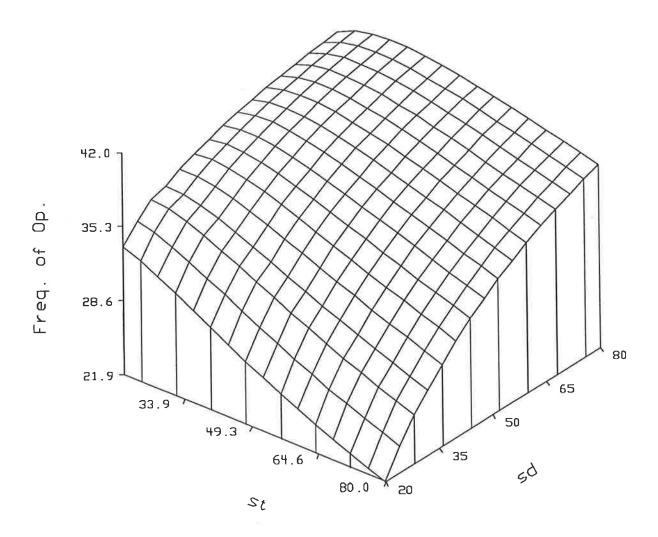

| 5.1 | ADVICE Results: Driver and transmission gate size vs. frequency      |

|     | (MHz)                                                                |

| 5.2 | Area × Delay products for the first three cases                      |

| 6.1 | Comparison of Utilization and optimum communications speed at dif-   |

|     | ferent failure rates                                                 |

| 6.2 | Area effects of reconfiguration wiring and switching overhead 201    |

| 6.3 | E(P) of 100 mm square arrays with different reconfiguration schemes. |

|     | $D_0 = 0.03 \text{ defects/mm}^2$ . Switch size is 5                 |

| 6.4 | E(P) of 100 mm square arrays with different reconfiguration schemes. |

|     | $D_0 = 0.03 \text{ defects/mm}^2$ . Switch size is 1                 |

| 6.5 | Comparison of different schemes with switch size=5 206               |

| 6.6 | Comparison of different schemes with switch size= 1 207              |

| 6.7 | Comparison of different schemes with switch size=1 208               |

### Acknowledgements

As no man is an island, no PhD thesis is completed in isolation, and I wish to thank all of those who contributed to the environment in which this thesis was built. As many people contributed in one way or another to my finishing of this task, I am sure that you all are not covered. Apologies to those I have missed.

First of all thanks to my supervisor, Kamran Eshraghian, whose boundless enthusiasm and energy, even in the face of adversity, has always impressed me. His paving of the road to the end of this task is much appreciated. Thanks also to Pat Clarke, of the Australian Defence Science and Technology Organisation, a true scientist, with a deep curiousity for all things mathematical. I am very grateful to Pat for his suggestions. Now to the last, but not least, of the "Big Three", Stu Tewksbury of AT&T Bell Laboratories. Thanks for providing me the opportunity to work at AT&T Bell Laboratories, and thanks also for your ever ready optimism and help, both inside and outside my thesis.

Now to the team efforts. First of all back to AT&T Bell Laboratories in Holmdel, New Jersey. There a multitude of people gave me help, both technically, and also with the day to day problems of living in a foreign land. First, to Bryan Ackland, and his department. Their help was essential for the production of the "frame" wafers and I also thank them for their general stimulus. In particular I wish to thank Bob Clarke, Jo Othmer, Mehdi Hatamian, Glenn Cash, Jay O'Neill and Adriaan Ligtenberg. Others, at Bell Labs, that deserve to be thanked for their many useful discussions include Larry Hornak, Trevor Little, Tom Wik, Dave Beecham and Vijay Kumar. On the personal side I found many Americans helpful in the often difficult experience of living in the United States. As well as Bryan (who is actually Australian) and Stu I wish to particularly thank Miles Murdocca, Teri Lindstrom and Ruth Dossica (not of AT&T) for their help in this area.

Next to my colleagues here at the University of Adelaide. I wish to thank Micheal Liebelt for his invaluable help with the computing facilities here. I would like to also express my gratitude to Warren Marwood, and the TFB team (in particular John Rockliff, Alex Dickinson, Micheal Pope, Greg Zyner and Syd Fensom) for their stimulus and assistance. Additional thanks to the members of the FES for helping me to survive the PhD process.

Funding for this research was provided by AT&T Bell Laboratories and the Australian Defence Science and Technology Organisation and to them I am grateful.

Finally I would like to express gratitude to my family and to Sandra Whittle for

their critical personal support at various stages of this work.

### **Preface**

I hereby declare that this thesis contains no material which has been accepted for the award of any other degree or diploma in any University and that, to the best of my knowledge and belief, this thesis contains no material previously published or written by another person, except where due reference is made in the text of this thesis. I also consent to this thesis being made available for photocopying and loan.

P.D. Franzon

23 December, 1988.

# Chapter 1

# Introduction

The introduction of fault tolerance into VLSI gives a number of potential advantages:

- 1. The economic advantage of yield enhancement for large VLSI (or ULSI¹) chips.

- 2. The system advantage of being able to fabricate chips larger than currently economically possible. The ultimate goal here is making chips the size of wafers, or Wafer Scale Integration (WSI).

- 3. The lifetime advantage of being able to make systems that do not require physical repair. (Physical repair being defined here as repair requiring physical replacement of components.)

The first two of these are achieved by introducing a capacity for tolerating the failures that arise from manufacturing defects. This category of fault tolerance techniques are better referred to as *Defect Tolerance*. The requirements for defect tolerance in WSI are somewhat more stringent than those for smaller chips as the wafer yield would be zero without these techniques. Defect tolerance can be defined as [Saucier, 1986]:

A defect tolerant circuit is a circuit which meets its user's requirements (functional and parametric specifications) despite the presence of end of manufacturing defects.

The achievement of an increase in system life expectancy (the third possible advantage above) implies either a capability to tolerate field failures as they occur, or to electronically, preferably automatically, effect a repair. The first capability results in a highly reliable system that has a long Mean Time Between Failure (MTBF) or

<sup>&</sup>lt;sup>1</sup>Ultra Large Scale Integration [Meindl, 1984]

a high probability of surviving a mission. The second capability results in a highly available system which is down for repair the minimum amount of time possible. All of these fall under the scope of the definition of fault tolerant systems, depending on the system's requirements [Avizienis & Laprie, 1986]:

Fault Tolerance: How to provide, by redundancy, service complying with the specification in spite of faults having occurred or occurring.

Achieving ultrahigh reliability is generally a more difficult task than achieving high availability or defect tolerance. High reliability implies that errors are detected and corrected as they occur whilst the other two capabilities imply a test and repair function only. Furthermore, achieving high availability requires a capacity for field test and repair or reconfiguration. Field reconfiguration is not a requirement for defect tolerance.

The results of research reported in this thesis is mainly concerned with techniques applicable to Defect Tolerance. Particular reference is given to Wafer-Scale Integration, though the details of defect tolerance techniques for VLSI and ULSI chips are also discussed extensively.

Fault tolerance for ultra-high reliability will not be discussed in this thesis. Ultra-high reliability can be achieved using techniques that are extensions of the approaches to defect tolerance about to be discussed. Though these techniques are extensions of the defect tolerance approaches to be discussed (and these approaches can often be used to achieve ultrahigh reliability) they would only be used in special situations. The main reasons are that (1) other sources of low reliability are usually more significant, and (2) few situations justify the considerable effort and expense required.

Although defect tolerance is critical to its achievement, it is important to realize that WSI is as much a statement in packaging as in increasing chip integration. Mainstream VLSI packaging has essentially remained static to the point where the communications bandwidth on-chip has become more than an order of magnitude better than that can be achieved between chips [Katevenis, 1983]. WSI can be seen as one packaging alternative that overcomes this problem relatively economically.

## 1.1 Research Outline

In order to design for defect tolerance one needs both suitable models, to describe the fault situation, and suitable techniques, to 'repair' the faults. The main object of the research work reported on in this thesis was to produce such models and apply them to two classes of defect tolerance problems to determine the relative tradeoffs in the applicable techniques. Particular consideration was given to the determination and comparison of approaches to mesh arrays. The defect tolerant design of a VLSI chip has also been the subject of some attention.

In this thesis the following results from this research program are presented:

- An accurate yield model is presented for modeling defect tolerant arrays (Section 3.6.) This model offers three major contributions:

- 1. It uses an accurate function to model the distribution of defects amongst processors.

- 2. The model comes in two forms:—yield; and expected number of processors.

These forms are useful in different applications, as discussed in Section 3.6.

- 3. A method is presented for accounting for wiring faults in reconfigurable arrays (Section 3.10.) Previously most workers either ignored the possibility of wiring faults or exaggerated their effect by assuming they all were fatal.

The model was also extended to take account of faults clustering in processors.

- The yield model was applied to the design of a defect tolerant chip to determine its optimal redundancy (Section 3.7.)

- The yield model was also applied to some general cases of defect tolerant chips and wafers (Sections 3.8 and 3.9.) These studies demonstrated when defect tolerance can be usefully applied and indicated some of the trade-offs involved.

- A yield simulator was written and used to determine critical areas of chips. Its

design and usefulness is discussed in Sections 3.6 and 3.11.

- Taxonomies are suggested for the different techniques that can be applied to the problem of reconfiguring linear and mesh arrays (Chapter 4.) These taxonomies were found useful when comparing the different reconfiguration methods.

- Particular attention is given to maximizing the speed at which WSI mesh arrays

operate. A list of suitable techniques is given in Section 4.8. The application

of some of these techniques is discussed in Chapters 5 and 6.

- Appropriate metrics for comparing redundancy schemes were developed (Section 4.4 and Chapter 6.)

- A new scheme for reconfiguring mesh arrays was designed and fabricated. The

details of the scheme, its design, and lessons learnt during its production are presented in Chapter 5. Particular attention was paid to optimizing the scheme's

speed. Models were developed to determine the speed of a reconfigurable interconnect.

- The different redundancy approaches for mesh connected arrays were compared on the basis of utilization, speed and yield for a number of case studies. This work is described in Chapter 6. The case studies in particular indicated the relative desirable properties of the various approaches. As a result of these studies a number of new approaches to reconfiguring mesh arrays were formulated. A number of new hierarchical approaches are suggested and compared in Section 6.3. Two new approaches, aimed at maximizing speed, are suggested in Section 6.5.

Before proceeding to report the results of this research, as background material, the relative merits of WSI will be discussed in this chapter, and the current world status of WSI projects will be treated in the next. The subject of yield modeling will be reviewed at the beginning of Chapter 3. A summary of existing applicable techniques for the wafer scale integration of mesh, and other, arrays will be presented in part of Chapter 4 and at the start of Chapter 6.

## 1.2 Advanced Packaging Technologies

The are many factors driving the search for advanced packaging and interconnect technologies:

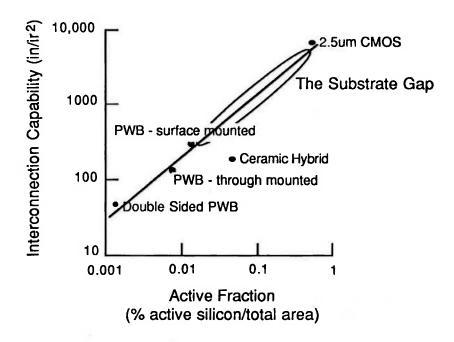

- The "substrate gap" [Knausenberger & Schaper, 1984] in interconnect capability between Silicon and Printed Circuit Boards (PCBs).

- The cost savings that can be incurred by reducing the power required by onchip drivers to drive off-chip interconnect. This has been exacerbated by the movement of mainstream IC technology to CMOS, with its lower driving capability.

- The growing mismatch between in-chip wiring density/performance and interchip wiring density/performance. In achieving VLSI most of the system is actually packaged in the IC medium whereas previously, with LSI and MSI,

Figure 1.1: Substrate efficiency

most of the system was packaged in the PCB medium. With the majority of the system packaged in the high performance medium the mismatch becomes more noticeable.

W.H. Knausenberger and L.W. Schaper of AT&T coined the term "substrate gap" when they considered the *substrate efficiency* of various interconnect substrates [Knausenberger & Schaper, 1984]. "Substrate efficiency" refers to how much active silicon can be placed on a given substrate. They defined a substrate efficiency figure of merit F:

$$F = \frac{\text{active silicon area}}{\text{total substrate area}} \tag{1.1}$$

They then plotted the interconnection capability, defined as the length of wire that can be placed in an area of substrate against this percentage. This plot is duplicated in Figure 1.1 and there the wiring density vs. active circuit density gap is self apparent.

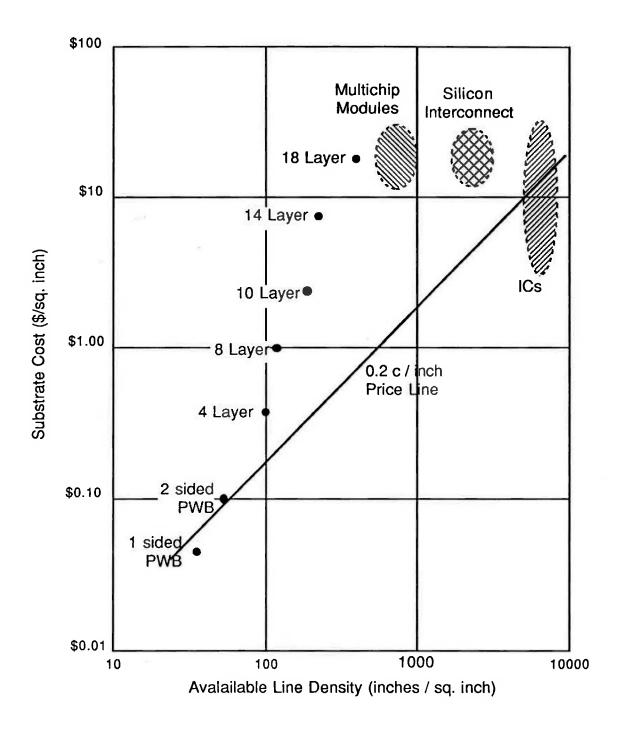

Taking this and other data, Messner has produced results that confirm this concept of a "substrate gap" [Messner, 1987]. As well as following interconnection density vs. active density arguments he determined the cost density relationships for various interconnection technologies. In constructing this model he described a cost per unit length of interconnect "price bulge", as illustrated in Figure 1.2.

Figure 1.2: Cost-density relationships for different interconnect media.

| Packaging Approach                               | Power × Delay | Size/<br>Weight | Cost | Overall<br>Figure of Merit |

|--------------------------------------------------|---------------|-----------------|------|----------------------------|

| Printed Wiring Board                             | 1.00          | 1.00            | 1.00 | 1.00                       |

| Thick Film Multi-Layer on Ceramic                | 1.08          | 0.42            | 1.02 | 0.46                       |

| Ceramic Multi-Layer<br>Hybrid                    | 0.34          | 0.20            | 0.65 | 0.044                      |

| Thin Film Single-<br>Sided Multi Layer<br>Hybrid | 0.19          | 0.14            | 0.60 | 0.016                      |

| Wafer Scale Int.                                 | 0.10          | 0.09            | 0.46 | 0.0041                     |

| Thin Film Double-<br>Sided Multi Layer<br>Hybrid | 0.08          | 0.07            | 0.44 | 0.0025                     |

Table 1.1: Comparison of Packages Figures of Merit

The "price bulge" occurs above the constant price per interconnect line of 0.2 cents/inch. Messner suggested that it was only because ICs and double sided PCBs were on this line that they were the primary media used in mass market consumer products. From this graph it can be seen that developing new interconnect media using silicon or ceramic hybrids are likely to return more cost benefit than the continual development of ever more expensive multilayer PCBs.

Neugebauer has compared a number of different packaging choices for a system with an operating speed of 100MHz [Neugebauer, 1984]. Doing this he determined some rough figures of merit for various important factors, which are repeated in Table 1.1. The main factor in determining the figures for Power x Delay and Cost were the extra driver power requirements for maintaining 100MHz. The cost figure was derived from the assumption that the main packaging cost of a system was determined by the cooling and power supply requirements.

Scaling worsens these problems. It is well known that on-chip interconnect speeds do not scale proportionally to on-chip feature sizes [Meindl, 1984]. Local interconnection speeds remain constant with scaling whilst long distance interconnections get worse as die sizes increase and line widths decrease. This same effect will impact inter

chip communications as well. Thus the power costs of driving inter chip connections will get proportionally worse with scaling unless lower capacitance connections are introduced.

Viewed as a transmission line, conventional PCB interconnects perform quite well with a bandwidth of around 250MHz [Ambekar et al., 1987,Rainal, 1979] and propagation delays of better than 190 ps/inch [Deierling, 1987]. In fact, as a transmission line, it performs better than silicon or ceramic based interconnect due to its lower substrate dielectric constant [Chong & McEnroe, 1985]. The substrate gap arises on density, cost and power considerations, rather than pure speed.

Until recently high speed system packages have generally been produced using expensive combinations of low gate count LSI chips and ultracompact packaging [Blodgett & Barbour, 1982] [Watari, 1987]. However as the functionality and speed of CMOS increases there will be a growing need for high speed packaging for these VLSI technologies. As can be seen in Table 1.1 the thin film interconnect technologies of WSI and thin film hybrids have more merit than the more traditional thick film technologies for high speed VLSI and ULSI.

#### 1.3 Potential Benefits of WSI

The potential benefits of WSI, particularly when compared with conventional systems approaches, are listed below in decreasing order of importance. Where appropriate, comparison will also be made with other thin film approaches.

## 1.3.1 Size and Weight

The integration of several million transistors onto a single wafer leads to an obvious size and weight advantage. For example in the ESPRIT 824 project [Ivey, 1987] a SIMD WSI array has been developed that achieves a scale of integration in which a single wafer replaces ten boards of conventional chips. The reduced cooling and power supply requirements of a WSI system [Neugebauer, 1984] contributes towards smaller size and lower weight. The aerospace industry can, in particular, benefit from products with these advantages. Other thin film packaging approaches can be similarly placed for size and weight.

#### 1.3.2 Reliability

The reliability advantages of WSI are clear and substantial also. A study of Naval Avionics systems failures [Robinson & Sauve, 1977] indicated that:

- 1. IC components were involved in less than two percent of all avionics failures.

- 2. Approximately *sixty percent* of all avionics failures were attributable to connector and cabling failure.

- 3. Twenty-Five percent of the failures were caused by maintenance and test procedures.

- 4. Thirteen percent were due to overstress and abuse of system components.

Although avionics is a physically harsh environment the conclusion can still be drawn that the most significant contribution new packaging techniques can make to improved systems reliability is to reduce the number of physical connectors required [Chaturvedi, 1988]. WSI achieves this to a significant degree indeed.

This conclusion can also be drawn from other sources using data gathered from telecommunications applications. There it has been found that the IC failure rate is roughly independent of the number of gates per chip [Hoover, Jr. et al., 1987]. A typical rate may be 50 FIT (failures in 10° hours) On the other hand the failure rate of external interconnections is directly proportional to their number at approximately 0.05 FIT per interconnection. In [Hoover, Jr. et al., 1987] it was concluded that a 10 times increase in the number of gates per IC results in a roughly similar increase in reliability for a constant sized system. (The FIT rates quoted are approximate only as they are influenced heavily by environment. For example, IC failure rates increase by a factor of two for every 10°C [Mahalingam, 1985]. The failure rate for package connections depends largely on the number of thermal cycles the connections go through. For example, a 40 pin leadless chip carrier can withstand between 2,000 and 5,000 thermal cycles between failures for 1 watt dissipation [Deierling, 1987].)

It would be expected that WSI would maintain this advantage over hybrid technologies. No figures are as yet available on the reliability of solder bump and other advanced hybrid connection technologies. IBM's thermal conduction modules, which employ solder bump techniques on LSI chips, are reputedly very reliable however.

WSI may also result in a higher availability than other packaging approaches. Many of the techniques used to implement defect tolerance are capable of being repeated later to effect a field repair if so desired. This may not seem important given the two percent figure in point 1 above but does have an impact when one considers burn-in failures. Typically more ICs fail during burn-in than during their first five years of operation [Little, 1986]. This means that any re-repair capacity results in some economic advantage.

Not only may the reconfigurability of WSI lead to higher burn-in survivability and higher reliability but, depending on the actual implementation, it may also result in reduced maintenance costs. As the repair process is highly automated, repair turn-around would be shorter and higher availability would be the result.

#### 1.3.3 Reduced Power Requirements

As mentioned in section 1.2 substantially reduced power would be required by WSI drivers. However the power density of such systems could be higher thus creating a different heat dissipation problem possibly requiring advanced cooling techniques. Other thin film packaging techniques would be similarly placed.

#### 1.3.4 Performance

There is significant potential for performance enhancement due to the lower capacitance and higher density of connections available. This potential may be reduced however when the overheads required to achieve the necessary defect tolerance are included. It would be expected that thin film hybrids would enjoy a similar advantage.

#### 1.3.5 Production Costs

Reductions in production costs stem from reduced packaging, power supply and cooling needs. Any possible reduction may vary on a project by project basis however. For example, extra costs may be introduced in handling higher cooling density requirements. Costs may also be incurred in unusual areas such as in carrying out the reconfiguration steps required.

An additional cost factor is the development cost. It may be usual that a WSI product would have a smaller market volume than many VLSI products and thus the already (probably higher) development cost must be amortized over a smaller production run.

The processing costs of thin film hybrids would be expected to be higher than for other packaging approaches.

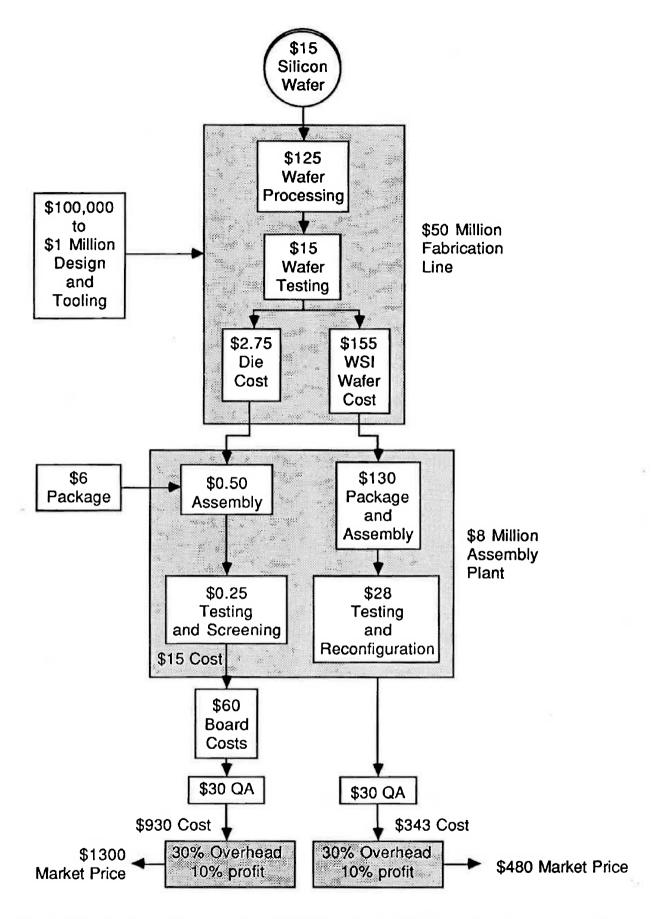

A rough cost comparison of populating a board with VLSI components compared with producing a WSI product with a similar capability is given in Figure 1.3. The costs of manufacturing and packaging the VLSI components are taken from [Dicken, 1988]. The manufacturing and Quality Assurance costs are based on an Australian manufacturer's experience<sup>2</sup>. The wafer scale costs for testing and reconfiguration are estimates. In the example taken from [Dicken, 1988] each wafer yielded 56 working dies on average (calculated as the wafer cost divided by the die cost.) It is assumed for the wafer scale case that each wafer yields a number of processors with a similar functionality. The basis for this assumption is the reasonable expectation that the increase in functionality resulting from the extra area gained from the loss of the pads and inter-die kerfs is precisely matched by the area lost to the reconfiguration wiring and those processors that can't be included in the array due to limitations in the reconfiguration wiring's flexibility. It is further assumed, pessimistically, that the packaging and assembly costs are together twenty times worse than that of a single die and the testing and screening cost is the same as the wafer cut into die. These costs depend a lot on the details of the function being implemented. It is also assumed that the reconfiguration step costs the same as the testing step. It would be expected that a similar level of equipment and time would be involved in both of these steps. The bottom line is that the WSI based product ships at about one-third of the cost of the equivalent conventionally packaged product. This is not too dissimilar to the cost comparison calculated for Table 1.1. Neugebauer's method for determining cost was largely based on the assumption that supplying power and dissipating the resultant heat was the major cost component. In Figure 1.3 actual production costs are considered and simple cooling requirements are assumed.

## 1.4 Difficulties to be Overcome to achieve WSI

A typical wafer would be expected to contain 100 or so defects manifesting themselves as faults. The main problem to be solved in achieving WSI is to introduce sufficient defect tolerance to handle this number of faults.

Architecturally, this is a sizable constraint. Usually, the accepted solution is to fabricate an array of similar elements with a large number of spares. The object is to reconfigure these spares into and out of the system to get a working wafer. Some form of Reconfiguration Scheme is required to do this and this introduces a silicon

<sup>&</sup>lt;sup>2</sup>Transponder Australia

Figure 1.3: Broad brush comparison of (\$US) costs for a WSI based product compared with the equivalent discrete die and board based product.

area and performance overhead. Judging the effects of these overheads and trading them off against the efficiencies of reconfiguration schemes will be examined for mesh arrays in Chapter 6.

Other problems that may create difficulty for a WSI product include:

- Possibly higher heat dissipation density requiring special packaging techniques;

- Possibly very high pin out count, again requiring special packaging;

- Increased design and development time;

- Smaller production runs;

- Difficult on-wafer power distribution and electromigration;

- Increased signal noise and crosstalk.

## 1.5 Hybrid WSI

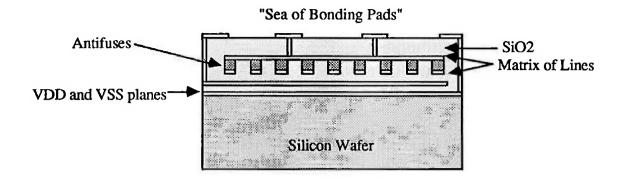

As indicated in Table 1.1 thin film hybrids offer many of the advantages of WSI. Furthermore thin film hybrids do not suffer from the architectural limitations outlined in Section 1.4. One class of hybrid that has become of increasing interest in recent times are hybrids with silicon as their substrate. Given their closeness to WSI the techniques used to produce these hybrids are often referred to as Hybrid Wafer Scale Integration (HWSI), though the "H" may sometimes be dropped.

Silicon hybrids offer a number of advantages over ceramic hybrids or advanced PC boards [Lyman, 1987]. Using well established IC processing techniques, the silicon substrate can easily accommodate 10 to  $25\mu m$  conductors compared with the  $75\mu m$  conductors of most advanced PC boards or ceramic hybrids. This could reduce the interconnect area to less than 1/10 that of standard boards or hybrids.

With shorter wiring runs parasitic inductance and capacitance would be reduced. Also passive elements such as bypass capacitors and terminating resistors can be fabricated on the substrate.

Silicon hybrids also have the important advantage that the thermal coefficients of expansion of the substrate and mounted chips are the same. This results in significantly reduced mechanical thermal stresses. This is particularly advantageous for operating at liquid nitrogen temperatures. Here the performance of CMOS parts exceeds that of bipolar parts at room temperature [Johnson, 1984].

However higher IC densities can lead to higher thermal dissipation densities. Fortunately silicon is a good conductor of heat and it is easy to glue metal or silicon carbide heat sinks to the substrate, thus alleviating this potential problem.

## 1.6 Three Dimensional Packaging

The concept of placing subsystems on silicon wafers leads naturally to the idea of forming complete systems in this medium. Wafers could be connected through the edges only. However if the wafers could be stacked and inter-wafer communication made possible through the stack significant advantages may be gained. The concept of, and current projects in, three dimensional packaging and three dimensional communications will be discussed in Section 2.4.

# Chapter 2

## World Status of WSI

The concept of wafer scale integration is an attractive one and has been around for almost as long as ICs have. However it wasn't until the late 1970s that the practical limitations of WSI were appreciated and appropriate methodologies developed. This chapter presents a brief history of WSI followed by a summary of major WSI projects. Only projects resulting in, or intending to result in, actual wafers or large area chips will be described.

Current Hybrid WSI projects and current investigations into three dimensional packaging will also be presented.

## 2.1 History of WSI

The history of WSI can be divided into three periods:

1964-1970 In these early days of WSI (even before the name had been coined!) the intention was to carry out the transition from SSI to MSI and possibly even LSI in a single step. The technological means for doing this were largely developed at Texas Instruments [Lathrop et al., 1967]. They developed the technique of discretionary wiring (where a unique final wiring pattern was produced for each wafer) as the means for reconfiguring the wafer after probe testing. The cost however of making a unique mask for each wafer precluded commercialization of the concept. Little work was carried out in this area until 1977.

1977-1984 The renaissance of WSI started in 1977/78 with three important papers that re-awoke interest in the area [Finilla & Love, 1977] [Manning, 1977] [Aubusson & Catt, 1978]. In his paper, Aubusson coined the phrase "Wafer

Scale Integration". In the early 1980s there were several attempts at developing wafer scale products, the most notable of which was Trilogy's attempt to put an IBM 3081 processor on an ECL wafer [Peltzer, 1983]. Although unsuccessful, they provided much insight into the understanding of some of the problems associated with this technology. There were also a lot of academic research on the subject of WSI during this period.

1984— This period, which is continuing today, marks the maturation of WSI technology. In particular several projects have been initiated which cope realistically with the limitations of WSI. Several researchers have also pursued investigations into the possibility of Hybrid WSI (silicon on silicon hybrids) as a means of achieving some of WSI's advantages whilst avoiding the constraints required for full WSI.

## 2.2 Major WSI Projects

Listed below are the major WSI projects, past and present, that have reached my attention. Projects that have resulted in little published information will of course be missing from this list. For example, IBM has been reported several times as having some form of WSI effort [Cole, 1985][ICC, 1987] but have never announced any details. Only projects that resulted in the fabrication of some representative device will be described.

## Discretionary Wiring Techniques

The first attempt at WSI was developed largely at Texas Instruments and eventually produced wafers [Lathrop et al., 1967]. The discretionary wiring technique involves making a unique mask for each wafer that can be used to connect together those circuits that work. Unfortunately, though many wafers worked, the cost of making a unique mask for almost every wafer hindered the concept from becoming a commercial reality. A methodology was developed to reduce the number of unique masks required [Calhoun, 1969] [Calhoun & MacNamee, 1972] but this approach was still insufficient to achieve commercial practicability.

### Memory and Large Chip Efforts: NTT

Nippon Telephone and Telegraph has had a long interest in defect tolerance techniques. Three memory WSI wafers were fabricated in the late 1970s and the early 1980s [Kitano et al., 1980] [Egawa et al., 1980] [Ueko et al., 1984]. More recently they have designed and fabricated a 37mm by 21mm sorting chip [Tsuda & Satoh, 1987].

### WSI Processor: Trilogy

In the early 1980s Trilogy attempted to put an IBM 3081 CPU onto an ECL wafer [Peltzer, 1983] [Amdahl, 1984]. Unfortunately, the effort met with failure primarily as a result of a combination of technical difficulties. Trilogy was trying out a new design methodology while bringing up a new process line at the same time. In attempting to do all of this at once they found the combination of achieving an appropriate balance between high defect counts, maintaining sufficient redundancy for an economic wafer yield, and achieving high speeds beyond the technical resources of the company [Jones, 1987] [Fischetti, 1984].

Nevertheless Trilogy still believes that they would have succeeded in the end though the extra effort and delay would most likely have made their product unprofitable [Fischetti, 1984].

#### VHSIC Phase 2 and TRW

The U.S. Department of Defence's Very High Speed Integrated Circuit (VHSIC) program has entered its second phase where the aim is to obtain a 20 fold performance improvement over the Phase-1 microcircuits [Klass, 1986]. It is intended that this performance improvement be obtained by decreasing the minimum feature size to  $0.5\mu m$ , increasing the speed to 100MHz and increasing the circuit density to to over 100,000 gates for 9mm square chips.

Two of the VHSIC Phase-2 contractors, IBM and Honeywell, aim to achieve these objectives by fabricating 9mm square CMOS or TTL chips and packaging the chips on small (100mm or less) ceramic hybrid boards. (Honeywell also has a separate silicon hybrid program.) TRW, on the other hand, is taking a more aggressive approach and fabricating 36mm square "superchips" in TTL and CMOS to achieve their goals [Ele, 1986]. A list of the superchips is given in Table 2.1. Each superchip is either one quarter or one third of a complete wafer.

| Chip Type                 | Process | total<br>devices<br>(M) | usable<br>devices<br>(M) | chip size<br>(in.) | yield<br>% | power<br>(W) | status   |

|---------------------------|---------|-------------------------|--------------------------|--------------------|------------|--------------|----------|

| FFT                       | bipolar | 3.9                     | 2.2                      | 1.4 by 1.4         | <b>3</b> 8 | 7.8–16.7     | optional |

| 2 Mb<br>four port<br>SRAM | CMOS    | 27.9                    | 18.8                     | 1.4 by 1.4         | 50         | 4            | funded   |

| Signal<br>Processor       | CMOS    | 27.9                    | 9.8                      | 1.4 by 1.4         | 29         | 7.9          | funded   |

| Data<br>Processor         | CMOS    | 34.7                    | 21.7                     | 1.4 by 1.8         | 20         | 8.5          | optional |

| Associative<br>Processor  | CMOS    | 10.1                    | 7.1                      | 1.4 by 1.4         | 45         | 9.5          | optional |

| Convolver<br>Correlator   | bipolar | 10                      | 6.2                      | 1.4 by 1.8         | 42         | 14.5         | funded   |

Table 2.1: TRW's superchip set

Unfortunately processing problems have so far prevented TRW from accomplishing their initial superchip aims. It was originally intended that E-beam techniques would be used to provide trench isolation in their  $0.5\mu m$  CMOS process. However they were never able to do this repeatably so their aims had to be scaled down [Waller, 1988]. Instead of fabricating a 27.9 million transistor CMOS signal processor a 4 million transistor processor has instead been fabricated on a 1.3 in. by 1 in. die. The two designs are essentially the same except that the latter has no on-board RAM.

TRW has not released details of the defect tolerance techniques employed but it appears that the nonreplicated modules are using Triple Modular Redundancy (TMR) and the replicated modules have spares that can be configured in via 'soft' reprogrammable switches. The use of soft switches for reconfiguration means that the system can also be reconfigured in the field. These techniques bring the anticipated

yields up from an estimated 10% (with an expected 200 to 250 defects per square centimeter) to the figures given in Table 2.1.

The elements of the superchip set are all self testing with the test circuits occupying from 18% to 25% of the total chip area. The remainder of the difference between "usable devices" and "total devices" is probably used for spares.

Even with the heat densities indicated in Table 2.1 no packaging problems are anticipated.

### WSI Disk

Formerly known as Sinclair Research [Inf, 1984], Anamartic's plans are to concentrate on what they perceive to be a market for WSI memory components.

It has long been recognized that between primary memory and disk memory there exist large gaps in terms of access time and cost per bit. Bubble memories were developed in an attempt to fill this gap. Anamartic perceive WSI based memories as succeeding here [Wilkinson, 1987].

Their studies have shown that a WSI based disk replacement unit would be cheaper than one based on conventional DRAM chip/PCB mount technology and would be more compact than one based on high density hybrid packaging techniques. Thus they see their WSI memories as providing a very high density memory unit that is more compact than primary memory whilst being faster and more reliable than disk memory. For compatibility they have made the interface to the WSI system look like a disk interface.

So far the company has fabricated a number of prototype wafers [Jesshope & Moore, 1986], which they will be enhancing with additional funding [Ele, 1987].

The company sees another possible market in applications where highly robust secondary memories are required.

## **RVLSI Program**

A technologically orientated WSI program has been on-going at MIT's Lincoln Laboratories for several years with U.S. Department of Defence funding. The program has been orientated at bringing into service techniques for restructuring wafers using laser fuses and antifuses.

In the Restructurable VLSI (RVLSI) program reconfiguration is performed by laser programming of an interconnection network laid out between processing elements. Initially the processing elements are not connected. After testing, fuses are blown and antifuse joins created in order to obtain a desired final connection pattern [Raffel, 1986] [Anderson, 1986]. The original fuses and antifuses required extra processing steps above those in normal fabrication lines [Wyatt et al., 1984] [Chapman, 1986] and have proven to be highly reliable. However the program now has designed a lower performance laser antifuse that does not require additional processing steps [Chapman et al., 1987].

The program has produced a number of wafers for signal processing applications which were mainly intended as technology demonstrators [Rhodes, 1986] [Gaverick & Pierce, 1983] [Raffel et al., 1985] [Mann & Rhodes, 1986]. More recently the group has branched into the fabrication of neural networks.

#### 2.2.1 ESPRIT 824 Program

This program is an European Economic Community funded venture into Wafer Scale Integration. Funded to the level of approximately \$US4.4M, with the industrial affiliates providing half of their own funding, this project spans four countries, six institutions and involves about 30 workers [Trilhe & Saucier, 1987].

In all of the proposed wafers, connections are to be made between working elements using CMOS transmission gates. Various technologies for programming these gates which are under investigation include:

- 1. Floating Gate FETs. E-beam programmed floating gate FETs are considered an attractive technology because of their high density and reprogrammability [Girard et al., 1987].

- 2. Laser fuses. The cutting of aluminium and polysilicon lines is a technique that leads to highly reliable open switches.

- 3. Serially programmed latches. The switches are programmed by serially fed in commands.

On many modern fabrication lines wafers are produced by stepping a scaled mask (usually containing a 10× magnified pattern) across the wafer. This creates a potential problem for a wafer scale part as it is desirable that some areas of the wafer have different masks than others, in particular around the periphery where the pads are. In the ESPRIT project this is solved by placing a set of unconnected pad drivers around the edge of the repeated 1:10 mask. A final 1:1 lower density wafer-wide

aluminium masking step is used to place the required peripheral pads and connect the required pad drivers only.

Another serious problem facing a wafer scale designer is that of distributing the required power over thin film aluminium without significant voltage drops and metal migration. One possible solution being investigated is the formation of a low cost, low resistance copper pattern on top of the passivation layer of the wafer [Barrett et al., 1986] [Barrett, 1987].

Three WSI designs are being planned for this project, namely a static RAM, a SIMD array and a defect tolerant microprocessor [Trilhe & Saucier, 1987].

#### 4.5 Mbit static RAM

This RAM will be implemented in a four inch  $1.25\mu m$  CMOS process like the other two projects. Unlike the Anamartic disk replacement it is logically organized as a conventional memory with 16 address lines.

#### SIMD Array

Intended mainly for image processing applications the aim of this project is to produce a 128 by 128 array of bit serial 30MHz Processing Elements (PEs) on a single wafer [Ivey et al., 1987]. This wafer has the capacity to replace 10 boards of conventional chips. An interesting facet of this scheme is that it will use a electron beam machine to test as well as to program the floating gates. Electron beam testing is normally considered uneconomic for VLSI design because of the excessive testing time required. However in this case the testing time is substantially reduced by using signature analysis, with all of the PE's signatures being produced in parallel, and then using the E-beam tester to read these otherwise difficult to access signatures. The E-beam tester, which is based on a scanning electron microscope, is then used to test the connections in parallel.

Each PE of the array consists of a serial adder/subtractor, two 64 bit RAMs and steering logic.

#### Large chip Microprocessor Based System

The motivation for this project is to develop a means for building large systems on a single large chip by (1) providing a set of building blocks, the primary block being a defect tolerant microprocessor [Genestier et al., 1986], and (2) providing a flexible interconnect in the form of a sea of gates. From these a microprocessor system that

can be dynamically reconfigured to meet changing requirements is produced. By providing different mixes of predefined building blocks a broad range of microprocessor based ASICs can be quickly developed.

## WSI Associative String Processor: Brunel University

The WSI Associative String Processor (WASP) is intended to be a wafer scale example of a homogeneous, reconfigurable and programmable, fine-grain parallel processing architecture [Lea, 1987][Lea, 1986] based on associative memories.